Metalloxidhalvledartransistorn eller MOS-transistorn är en grundläggande byggsten i logikchips, processorer och moderna digitala minnen. Det är en majoritetsbärare, där strömmen i en ledande kanal mellan källan och avloppet moduleras av en pålagd spänning till grinden. Denna MOS-transistor spelar en nyckelroll i olika analoga och blandade signal-IC:er. Denna transistor är ganska anpassningsbar, så den fungerar som en förstärkare, en switch eller en motstånd . inte transistorer klassificeras i två typer PMOS & NMOS. Så, den här artikeln diskuterar en översikt över NMOS transistor – tillverkning, krets och arbete.

Vad är en NMOS-transistor?

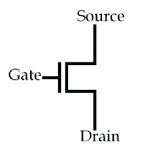

En NMOS-transistor (n-channel metal-oxide semiconductor) är en typ av transistor där dopämnen av n-typ används i grindområdet. En positiv (+ve) spänning på gateterminalen slår på enheten. Denna transistor används främst i CMOS (kompletterande metalloxid-halvledare) design & även i logik & minneschips. Jämfört med PMOS-transistorn är denna transistor mycket snabbare, så fler transistorer kan placeras på ett enda chip. NMOS-transistorsymbolen visas nedan.

Hur fungerar NMOS-transistorn?

NMOS-transistorns funktion är; när NMOS-transistorn tar emot en icke försumbar spänning så bildar den en sluten krets vilket innebär att anslutningen från source-terminalen till avloppet fungerar som en tråd. Så strömmen flyter från grindterminalen till källan. På liknande sätt, när denna transistor tar emot en spänning på ungefär 0V, bildar den en öppen krets vilket innebär att anslutningen från source-terminalen till drain kommer att brytas, så ström flyter från gate-terminalen till drain.

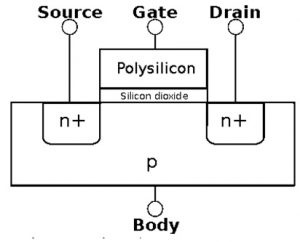

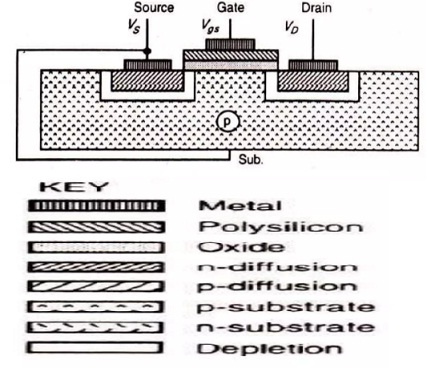

Tvärsnitt av NMOS-transistor

I allmänhet är en NMOS-transistor helt enkelt byggd med en p-typ kropp av två n-typ halvledarregioner som ligger intill grinden som kallas source & drain. Denna transistor har en styrande gate som styr elektronflödet mellan source & drain-terminalerna.

I denna transistor, eftersom transistorns kropp är jordad, är PN-övergångspunkterna för source & drain mot kroppen omvänt förspända. Om spänningen vid grindterminalen ökas kommer ett elektriskt fält att börja öka och attraherar fria elektroner till basen av Si-SiO2-gränssnittet.

När spänningen är tillräckligt hög kommer elektroner att sluta fylla alla hål och ett tunt område under grinden som kallas kanalen kommer att inverteras för att fungera som en halvledare av n-typ. Detta kommer att skapa en ledande bana från källterminalen till avloppet genom att tillåta strömflödet, så att transistorn slås PÅ. Om grindterminalen är jordad flyter ingen ström i den omvända förspända förbindelsen så transistorn kommer att stängas AV.

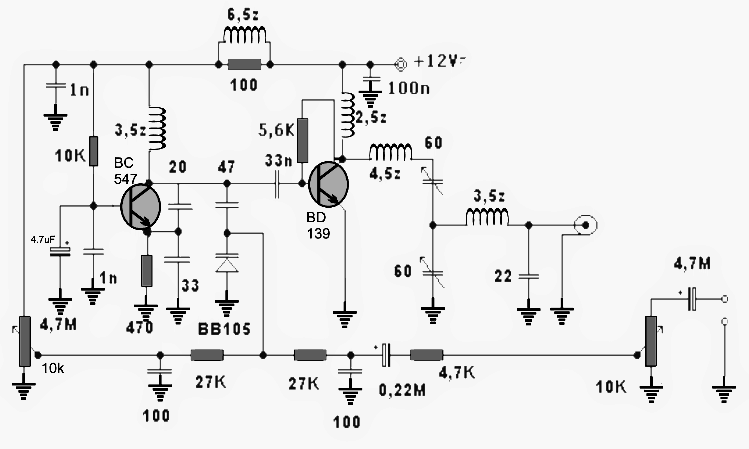

NMOS transistorkrets

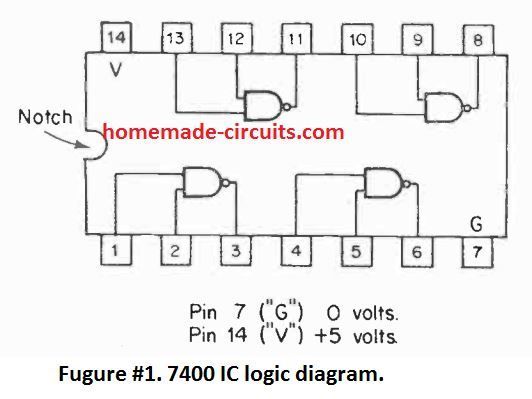

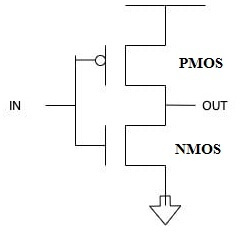

NOT-grinddesignen med PMOS- och NMOS-transistorer visas nedan. För att designa en NOT-grind måste vi kombinera pMOS- och nMOS-transistorer genom att ansluta en pMOS-transistor till källan och en nMOS-transistor till marken. Så kretsen kommer att vara vårt första CMOS-transistorexempel.

NOT-grinden är en typ av logisk grind som genererar en inverterad ingång som en utgång. Denna grind kallas också en inverter. Om ingången är '0' blir den inverterade utgången '1'.

När ingången är noll, går den till pMOS-transistorn på toppen & ner till nMOS-transistorn längst ner. När ingångsvärdet '0' når pMOS-transistorn, inverteras det till '1'. sålunda stoppas anslutningen mot källan. Så detta kommer att generera ett logiskt '1'-värde om anslutningen mot avloppet (GND) också är stängd. Vi vet att nMOS-transistorn inte kommer att invertera ingångsvärdet, därför tar den nollvärdet som det är och det kommer att göra en öppen krets till avloppet. Så ett logiskt ett-värde genereras för grinden.

På liknande sätt, om ingångsvärdet är '1' skickas detta värde till båda transistorerna i ovanstående krets. När '1'-värdet tar emot pMOS-transistorn, kommer den att inverteras till ett 'o'. som ett resultat är anslutningen till källan öppen. När nMOS-transistorn får värdet '1, kommer den inte att bli inverterad. så inmatningsvärdet förblir som ett. När ett värde väl har tagits emot av nMOS-transistorn stängs anslutningen mot GND. Så det kommer att generera en logisk '0' som en utgång.

Tillverkningsprocess

Det finns många steg involverade i NMOS-transistortillverkningsprocessen. Samma process kan användas för PMOS- och CMOS-transistorer. Det mest använda materialet i denna tillverkning är antingen polykisel eller metall. Steg-för-steg tillverkningsprocessen för NMOS-transistorn diskuteras nedan.

Steg 1:

Ett tunt lager av kiselskivor ändras till material av P-typ genom att helt enkelt dopa med bormaterial.

Steg 2:

Ett tjockt Sio2-lager odlas på ett komplett substrat av p-typ

Steg 3:

Nu är ytan belagd genom en fotoresist på det tjocka Sio2-skiktet.

Steg 4:

Efteråt exponeras detta lager för UV-ljus med en mask som beskriver de områden in i vilka diffusion ska ske tillsammans med transistorkanaler.

Steg 5:

Dessa områden etsas bort ömsesidigt med den underliggande Sio2 så att waferns yta exponeras inom fönstret som definieras genom masken.

Steg 6:

Den kvarvarande fotoresisten separeras och det tunna Sio2-skiktet odlas 0,1 mikrometer vanligtvis över hela chipets yta. Därefter placeras polykisel på denna för att bilda grindstrukturen. En fotoresist placeras på hela polykiselskiktet och exponerar ultraviolett ljus genom hela masken2.

Steg 7:

Genom att värma upp wafern till maximal temperatur uppnås diffusioner och passerar gas med önskade n-typ föroreningar som fosfor.

Steg 8:

En en mikrometers tjocklek av kiseldioxid odlas överallt och fotoresistmaterial placeras på den. Exponera det ultravioletta ljuset (UV) genom mask3 på de föredragna områdena av gate, käll- och dräneringsområden etsas för att göra kontaktsnitten.

Steg 9:

Nu placeras en metall som aluminium över dess en mikrometer breda yta. Återigen odlas ett fotoresistmaterial över hela metallen och utsätts för UV-ljus genom mask4 som är en etsad form av den obligatoriska sammankopplingsdesignen. Den slutliga NMOS-strukturen visas nedan.

PMOS vs NMOS transistor

Skillnaden mellan PMOS- och NMOS-transistorer diskuteras nedan.

| PMOS transistor | NMOS transistor |

| PMOS transistor står för P-kanal metall-oxid-halvledartransistor. | NMOS-transistor står för N-kanal metall-oxid-halvledartransistor. |

| Källa & drain i PMOS-transistorer är helt enkelt gjorda med n-typ halvledare | Källa & drain i NMOS-transistorn är helt enkelt gjorda med halvledare av p-typ. |

| Substratet för denna transistor är gjord med en halvledare av n-typ | Substratet för denna transistor är gjord med halvledare av p-typ |

| Majoriteten av laddningsbärare i PMOS är hål. | Majoriteten av laddningsbärarna i NMOS är elektroner. |

| Jämfört med NMOS är PMOS-enheter inte mindre. | NMOS-enheter är ganska mindre jämfört med PMOS-enheter. |

| PMOS-enheter kan inte bytas snabbare jämfört med NMOS-enheter. | Jämfört med PMOS-enheter kan NMOS-enheter bytas snabbare. |

| PMOS-transistorn kommer att leda när en låg spänning tillförs grinden. | NMOS-transistorn kommer att leda när en hög spänning tillförs grinden. |

| Dessa är mer immuna mot buller. | Jämfört med PMOS är dessa inte immuna mot brus. |

| Tröskelspänningen (Vth) för denna transistor är en negativ storhet. | Tröskelspänningen (Vth) för denna transistor är en positiv kvantitet. |

Egenskaper

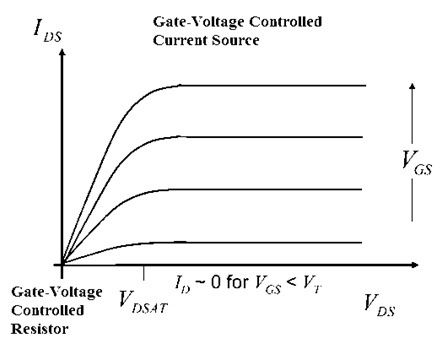

De I-V-egenskaper hos NMOS-transistorn visas nedan. Spänningen mellan grinden och källklämmorna 'V GS ’ & även mellan source & drain ’V DS ’. Så, kurvorna mellan I DS och V DS uppnås genom att helt enkelt jorda källans terminal, ställa in ett initialt VGS-värde och svepa V DS från '0' till det högsta DC-spänningsvärdet som ges av V DD när du trampar V GS värde från '0' till V DD . Så för extremt lågt V GS , jag DS är extremt små och kommer att ha en linjär trend. När V GS värdet blir högt, då jag DS förbättrar & kommer att ha nedanstående beroende av V GS & I DS ;

Om V GS är mindre än eller lika med V TH , då är transistorn i AV-läge och fungerar som en öppen krets.

Om V GS är större än V TH , då finns det två driftlägen.

Om V DS är mindre än V GS - I TH , då arbetar transistorn i linjärt läge och fungerar som ett motstånd (R PÅ ).

IDS = u eff C oxe W/L [(V GS - I TH )I DS – ½ V DS ^2]

Var,

'µeff' är laddningsbärarens effektiva rörlighet.

'COX' är kapacitansen för grindoxid för varje enhetsarea.

W & L är kanalens bredd och längd på motsvarande sätt. R PÅ värdet styrs helt enkelt av grindens spänning följer som;

R PÅ = 1/tum n C oxe W/L [(V GS - I TH )I DS – ½ V DS ^2]

Om VDS är större än eller lika med V GS - I TH , då fungerar transistorn i mättnadsläget

jag DS = u n C oxe W/L [(V GS - I TH )^2 (1+λ V DS ]

I den här regionen, när jag DS är högre, då är strömmen minimalt beroende av V DS värde, men dess högsta värde styrs helt enkelt genom VGS. Kanallängdsmoduleringen 'λ' står för höjningen inom IDS genom en ökning inom VDS i transistorer, på grund av pinch-off. Denna Pinch-off inträffar när både V DS och V GS besluta om det elektriska fältmönstret nära dräneringsområdet, vilket ändrar de naturliga laddningsbärarnas riktning. Denna effekt minskar den effektiva kanalens längd och ökar I DS . Helst är 'λ' ekvivalent med '0' så att I DS är helt oberoende av V DS värde inom mättnadsområdet.

Alltså handlar det här om en översikt över en NMOS transistor – tillverkning och krets med fungerande. NMOS-transistorer spelar en nyckelroll vid implementering av logiska grindar såväl som andra olika digitala kretsar. Detta är en mikroelektronisk krets som huvudsakligen används vid design av logiska kretsar, minneschips och i CMOS-design. De mest populära tillämpningarna av NMOS-transistorer är switchar och spänningsförstärkare. Här är en fråga till dig, vad är en PMOS-transistor?