I det här inlägget kommer vi att lära oss hur man bygger NOT, AND, NAND, OR och NOR logiska grindar med diskreta transistorer. Den största fördelen med att använda transistorlogiska grindar är att de kan fungera även med spänningar så låga som 1,5 V.

I vissa elektroniska applikationer kan den tillgängliga spänningen vara otillräcklig för att driva TTL eller till och med CMOS IC. Detta gäller särskilt för prylar som går på batterier. Utan tvekan har du alltid 3-volts logisk IC-alternativ. Dessa är dock inte alltid lättillgängliga för entusiasten eller experimenteraren, och de fungerar inte under sina definierade spänningsspecifikationer (vanligtvis under 2,5 volt DC).

Dessutom kanske det bara finns plats för ett enda 1,5-voltsbatteri i en batteridriven applikation. Ja, vad ska du göra då? Vanligtvis IC logiska grindar kan ersättas av transistoriserade logiska grindar. För varje speciell logikgrind krävs i allmänhet bara ett par transistorer, och för en typisk NOT-grind-inverterlogik krävs bara en transistor.

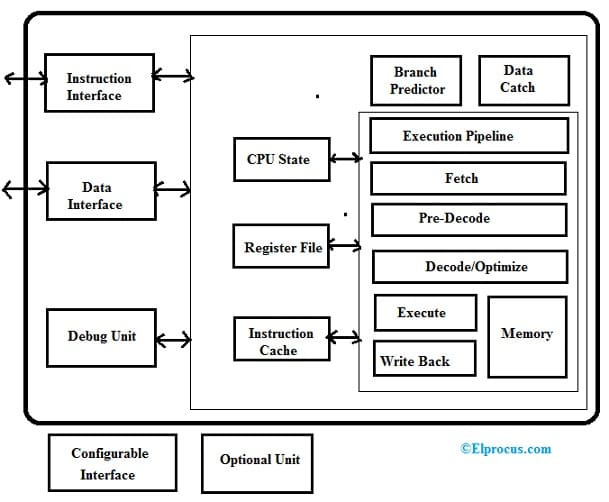

FETs kontra bipolär transistor

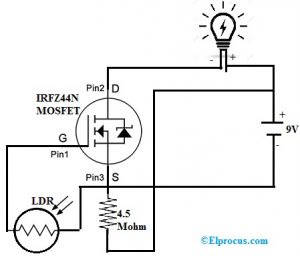

Fälteffekttransistorer (FET) vs bipolära transistorer : vilket är det bättre alternativet för lågspänningslogikkretsar? En stor egenskap hos FAKTA är att deras 'på' motstånd är otroligt lågt. Dessutom behöver de mycket låg gate-turn-on ström.

De har dock en begränsning i extremt lågspänningstillämpningar. Typiskt är grindspänningsgränsen en volt eller så. Vidare kan den tillgängliga spänningen minska under FET:s optimala arbetsområde om ett strömbegränsande eller neddragningsmotstånd är anslutet till grinden.

Omvänt har bipolära omkopplingstransistorer en fördel i applikationer med extremt låg spänning, enstaka batterier eftersom de bara behöver 0,6 till 0,7 volt för att slå på.

Dessutom är majoriteten av vanliga FET:er, som normalt säljs i bubbelförpackningar i din närmaste elektronikaffär, ofta dyrare än bipolära transistorer. Dessutom kan ett bulkpaket av bipolära transistorer i allmänhet köpas till priset av ett par FET.

FET-hantering kräver betydligt mer omsorg än bipolär transistorhantering. Elektrostatisk och allmän experimentell missbruk gör FET:er särskilt benägna att skadas. Brända komponenter kan förstöra en trevlig, kreativ kväll av experiment eller innovation, för att inte glömma den känslomässiga smärtan av felsökning.

Grunderna för att byta transistorer

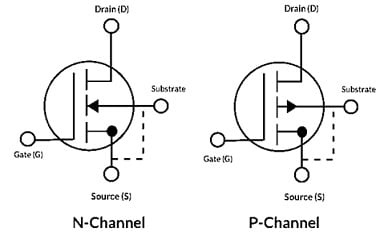

De logiska kretsexemplen som förklaras i den här artikeln använder sig av bipolära NPN-transistorer eftersom de är överkomliga och inte behöver speciell hantering. För att undvika att skada enheten eller de delar som stödjer den, bör lämpliga säkerhetsåtgärder vidtas innan du ansluter din krets.

Även om våra kretsar huvudsakligen är centrerade på bipolära kopplingstransistorer (BJT), kunde de lika väl ha konstruerats med FET-teknik.

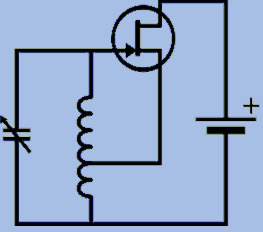

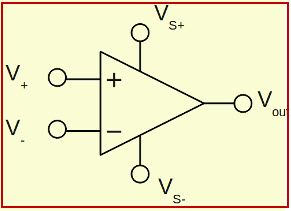

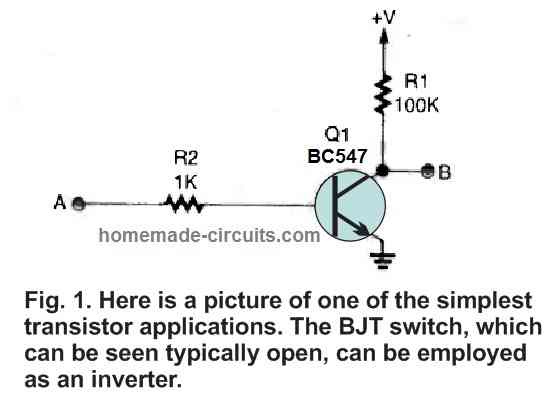

Den grundläggande switchkretsen är en enkel transistorapplikation, vilket är en av de enklaste designerna.

Att göra en NOT-port med en enkel transistor

En schematisk bild av transistoromkopplaren visas i figur 1. Beroende på hur den är implementerad i en speciell applikation kan omkopplaren ses som antingen hållen låg eller normalt öppen.

En enkel logikgrind för växelriktaren av typen NOT kan skapas av den enkla omkopplingskretsen som visas i fig. 1 (där punkt A är ingången). En NOT-grind fungerar på ett sådant sätt att om ingen DC-förspänning tillhandahålls till transistorns bas (punkt A; Q1), kommer den att förbli avstängd, vilket resulterar i en hög eller logisk 1 (lika med V+-nivå) vid utgången ( punkt B).

Emellertid aktiveras transistorn när den korrekta förspänningen tillhandahålls till basen av Q1, vilket trycker kretsens utgång lågt eller till logisk 0 (nästan lika med noll potential). Transistorn, betecknad Q1, är en bipolär transistor för allmänt bruk, eller en BC547, som vanligtvis används i lågeffektomkopplings- och förstärkartillämpningar.

Alla transistorer som är likvärdiga med den (som 2N2222, 2N4401, etc.) skulle fungera. R1 och R2:s värden valdes för att skapa en kompromiss mellan låg strömförbrukning och kompatibilitet. I alla utföranden är alla motstånden 1/4 watt, 5 % enheter.

Matningsspänningen är justerbar mellan 1,4 och 6 volt DC. Observera att kretsen kan fungera som en buffert när belastningsmotståndet och utgångsanslutningen skiftas till transistorns emitter.

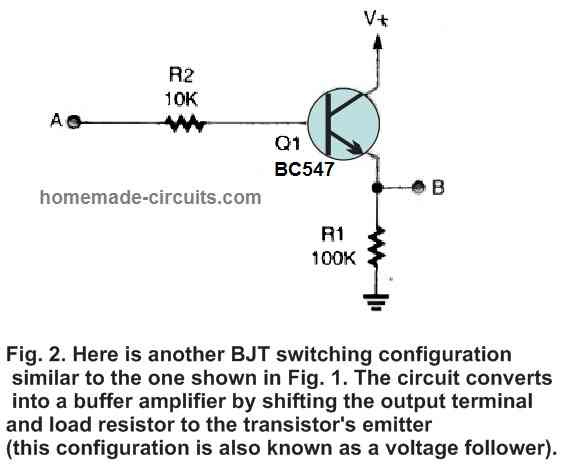

Att göra en buffertport med en enkel BC547 BJT

En spänningsföljare, eller buffertförstärkare, är en typ av logisk omkopplingskonfiguration identisk med den som visas i figur 2. Det bör noteras att belastningsmotståndet och utgångsterminalen har flyttats från transistorns kollektor till dess emitter i denna krets, som är den primära skillnaden mellan denna design och den som visas i fig. 1.

Transistorns funktion kan också 'vändas' genom att flytta belastningsmotståndet och utgångsterminalen till den andra änden av BJT.

Med andra ord, när ingen förspänning tillhandahålls till kretsens ingång, förblir utsignalen från kretsen låg; men när en förspänning av adekvat spänning tillförs kretsens ingång, blir utsignalen från kretsen hög. (Det är precis motsatsen till vad som händer i den tidigare kretsen.)

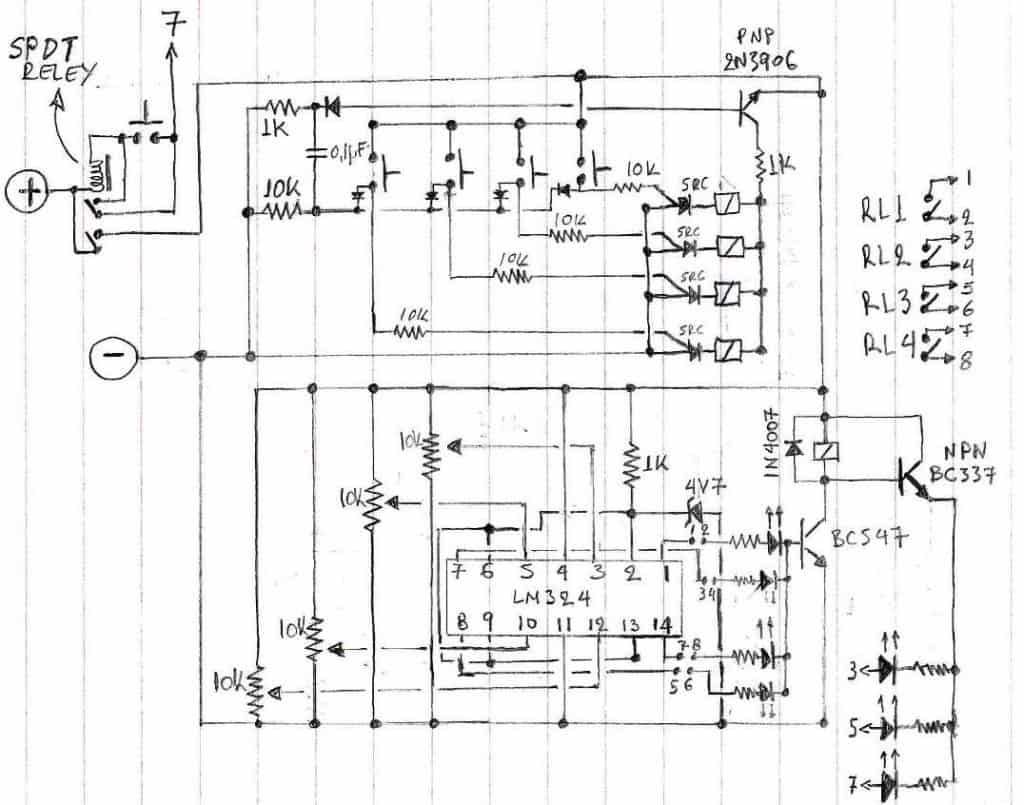

Designa två-ingångs logiska grindar med hjälp av transistorer

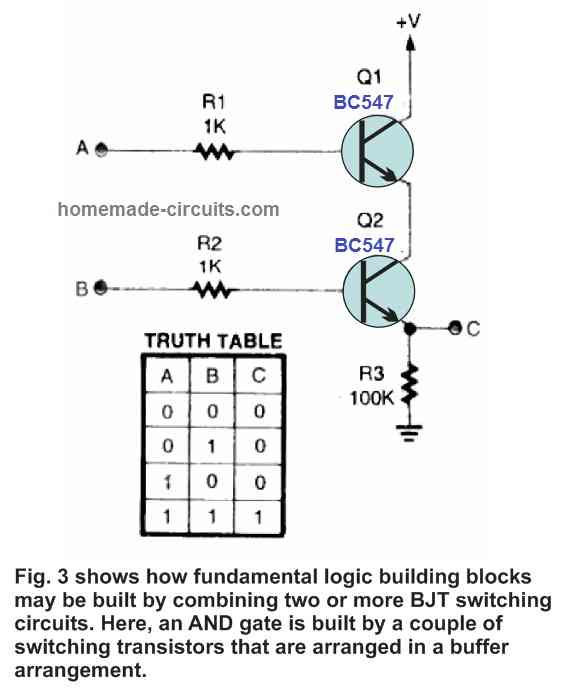

OCH Gate som använder två transistorer

Figur 3 illustrerar hur en grundläggande OCH-grind med två ingångar kan skapas med användning av ett par buffertar, tillsammans med sanningstabellen för den grinden. Sanningstabellen illustrerar vad utdataresultaten skulle vara för varje distinkt uppsättning indata. Punkterna A och B används som kretsens ingångar, och punkt C fungerar som kretsens utgång.

Det är viktigt att notera från sanningstabellen att bara en uppsättning ingångsparametrar resulterar i en logisk-hög utsignal, medan alla andra ingångskombinationer resulterar i en logisk-låg utsignal. Utsignalen från OCH-grinden i figur 3 förblir något under V+ när den väl blir hög.

Detta händer på grund av spänningsfallet mellan de två transistorerna (Q1 och Q2).

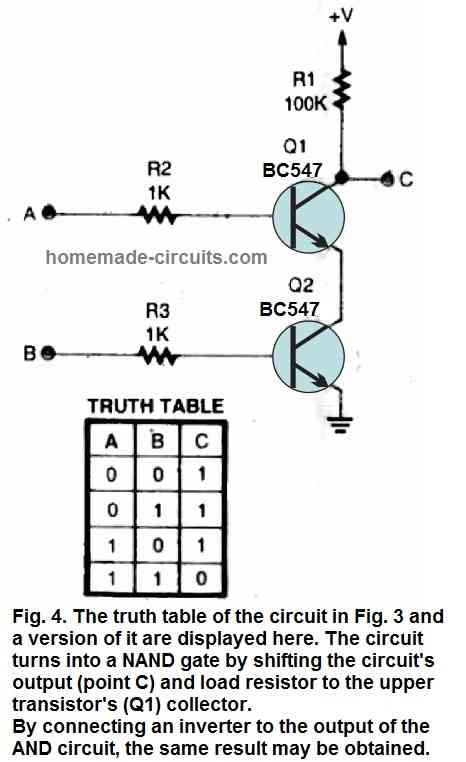

NAND-port som använder två transistorer

En annan variant av kretsen i figur 3 och tillhörande sanningstabell visas i figur 4. Kretsen förvandlas till en NAND-grind genom att förskjuta utgången (punkt C) och utgångsmotståndet till den övre transistorns (Q1) kollektor.

Eftersom både Q1 och Q2 måste slås PÅ för att dra den nedre sidan av R1 till jord, är spänningsförlusten vid utgång C obetydlig.

Om transistorn OCH eller transistorns NAND-grindar behöver mer än två ingångar, kan fler transistorer mycket väl anslutas i de visade designerna för att tillhandahålla tre, fyra, etc. ingångs-OCH eller NAND-grindar.

För att kompensera för de enskilda transistorernas spänningsförluster bör V+ dock ökas i motsvarande grad.

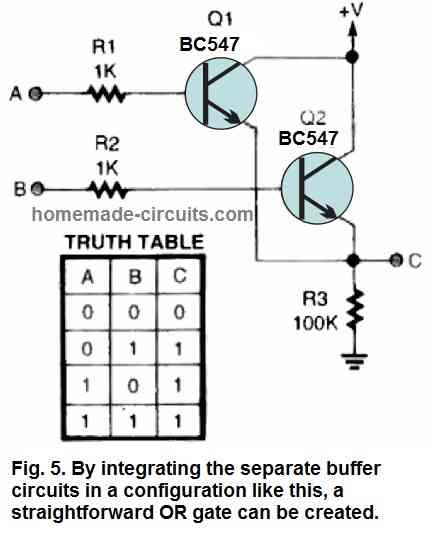

ELLER Gate som använder två transistorer

En annan form av logikkrets med två ingångar kan ses i figur 5, tillsammans med ELLER-grindkretsens sanningstabell.

Utsignalen från kretsen är hög när antingen ingång A eller ingång B trycks högt, men på grund av de kaskadkopplade transistorerna är spänningsfallet över 0,5 volt. Återigen indikerar de visade siffrorna att det finns tillräckligt med spänning och ström för att driva den efterföljande transistorgrinden.

NOR-port som använder två transistorer

Figur 6 visar nästa grind på vår lista, en NOR-port med två ingångar, tillsammans med dess sanningstabell. I likhet med hur AND- och NAND-grindar svarar på varandra, gör OR- och NOR-kretsar detsamma.

Var och en av de visade grindarna är kapabla att tillhandahålla tillräckligt med drivning för att aktivera åtminstone en eller flera intilliggande transistorgrindar.

Transistor Logic Gate-applikationer

Vad gör du med de ovan förklarade digitala kretsarna som du nu har? Allt som du kan åstadkomma med konventionella TTL- eller CMOS-grindar, men utan att oroa dig för spänningsbegränsningarna. Här är några tillämpningar av transistor-logiska grindar i aktion.

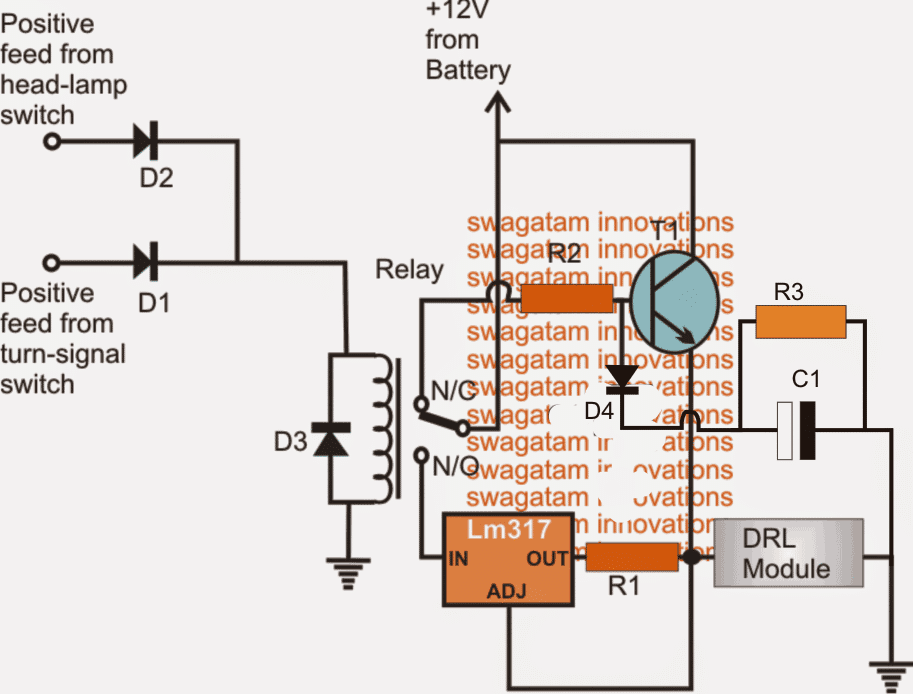

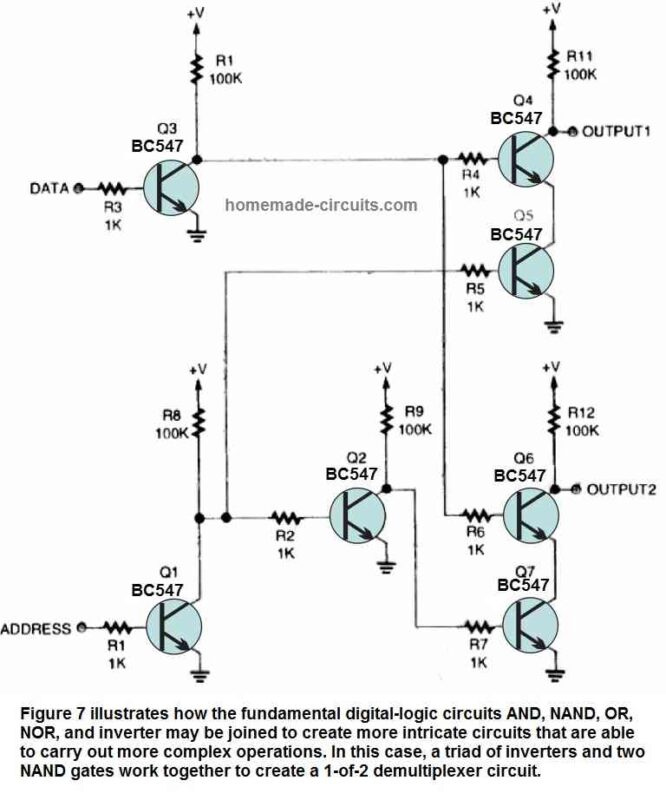

Demultiplexerkrets

En 1-av-2-demultiplexerare med tre NOT-grindar och två NAND-kretsar visas i figur 7. Den lämpliga utgången väljs med en-bits 'adressingång', som kan vara antingen OUTPUT1 eller OUTPUT2, medan drivinformationen appliceras till kretsen med hjälp av DATA-ingången.

Kretsen fungerar mest effektivt när datahastigheten hålls under 10 kHz. Kretsens funktionalitet är okomplicerad. DATA-ingången tillförs den erforderliga signalen, som sätter PÅ Q3 och inverterar inkommande data vid Q3:s samlare.

Utsignalen från Q1 drivs hög om ADDRESS-ingången är låg (jordad eller ingen signal tillhandahålls). Vid Q1:s kollektor är den höga effekten uppdelad i två banor. I den första vägen tillförs Q1:s utgång till Q5:s bas (en av benen på en NAND-grind med två ingångar), slår på den och 'aktiverar' därför NAND-grinden som består av Q4 och Q5.

I den andra vägen matas Q1:s höga utsignal samtidigt till ingången på en annan NOT-grind (Q2). Efter att ha genomgått en dubbel inversion blir Q2:s uteffekt låg. Denna låga matas till Q7:s bas (en terminal på en andra NAND-grind, som består av Q6 och Q7), vilket stänger av NAND-kretsen.

All information eller signal som tillförs DATA-ingången anländer till OUTPUT1 under dessa omständigheter. Alternativt vänds situationen om en hög signal ges till ADDRESS-ingången. Det betyder att all information som ges till kretsen kommer att visas vid OUTPUT2 eftersom Q4/Q5 NAND-grinden är inaktiverad och Q6/Q7 NAND-grinden är aktiverad.

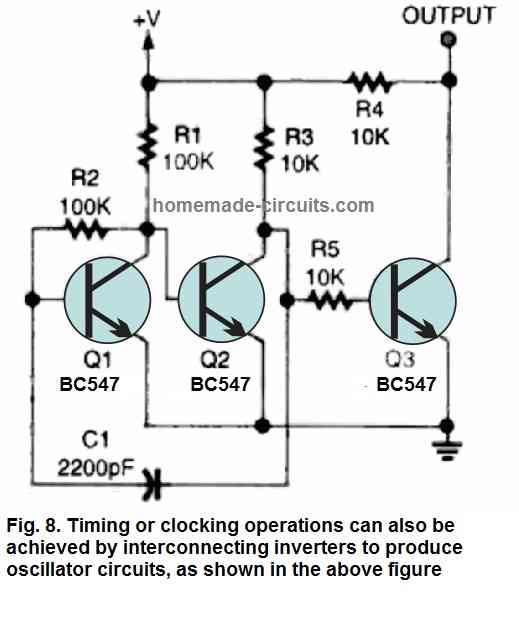

Oscillatorkrets (klockgenerator)

Vår nästa logikgrindapplikation för transistor, illustrerad i fig. 8, är en grundläggande klockgenerator (även känd som en oscillator) gjord av tre vanliga NOT-grindväxelriktare (varav en är förspänd med hjälp av ett återkopplingsmotstånd, R2, som sätter den i den analoga regionen).

För att kompensera utgången ingår en tredje NOT-grind (Q3) som levererar komplementet till oscillatorutgången. C1-värdet kan ökas eller minskas för att ändra kretsens driftfrekvens. Utgångsvågformen har en frekvens på cirka 7 kHz med V+ vid 1,5 volt DC, med de angivna komponentvärdena.

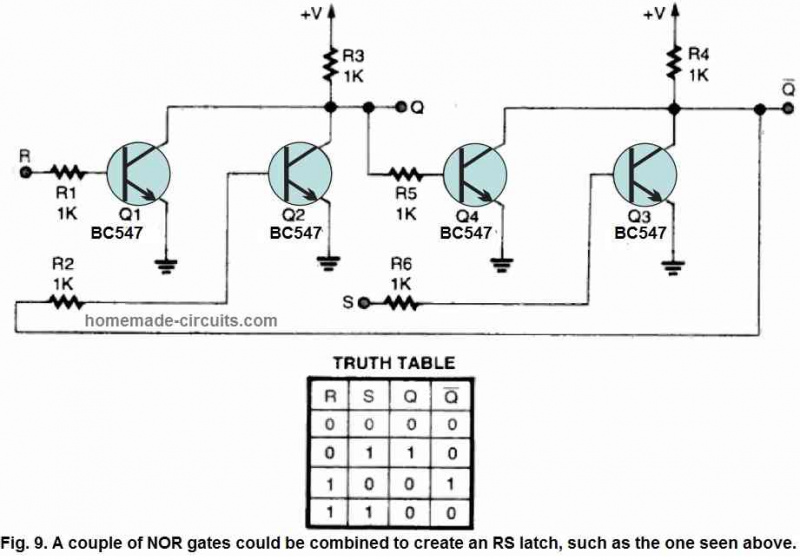

RS spärrkrets

Fig. 9 visar vår slutliga applikationskrets, en RS-lås uppbyggd av två NOR-grindar. För att säkerställa en sund utgångsdrift vid Q- och Q-utgångarna är motstånden R3 och R4 justerade till 1k ohm.

RS-låsets sanningstabell visas tillsammans med den schematiska designen. Det här är bara några illustrationer av de många pålitliga, lågspännings-, digitala, logiska grindkretsar som kan skapas med individuella transistorer.

Kretsar som använder transistoriserad logik behöver för många delar

Många problem kan lösas med alla dessa lågspänningstransistoriserade logiska kretsar. Men att använda för många av dessa transistoriserade grindar kan leda till nya problem.

Antalet transistorer och resistorer kan bli ganska stort om applikationen du bygger innehåller en stor mängd grindar som tar upp värdefullt utrymme.

Att använda transistormatriser (många transistorer inneslutna i plast) och SIP-motstånd (Single Inline Package) i stället för enskilda enheter är ett sätt att lösa detta problem.

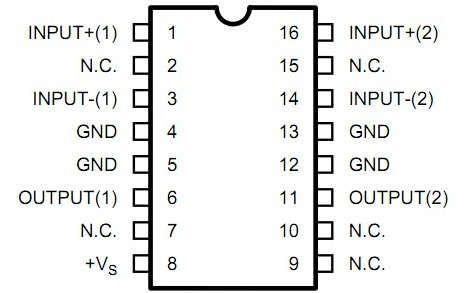

Ovanstående tillvägagångssätt kan spara ett ton utrymme på ett kretskort samtidigt som det bibehåller prestanda lika med deras ekvivalenter i full storlek. Transistormatriser erbjuds i ytmonterade, 14-stifts genomgående hål och fyrkantiga förpackningar.

För de flesta kretsar kan blandningstransistortyper vara helt acceptabelt.

Ändå är det tillrådligt att försöksledaren arbetar med en enda typ av transistor för att bygga de transistoriserade logiska kretsarna (vilket innebär att om du skapar en sektion av en grind med BC547, försök sedan använda samma BJT för att göra de andra återstående grindarna också).

Resonemanget är att olika transistorvarianter kan ha något olika egenskaper och därmed kan bete sig olika.

Till exempel, för vissa transistorer kan basinkopplingsgränsen vara större eller mindre än en annan, eller en kan ha en total strömförstärkning som är lite högre eller lägre.

Å andra sidan kan kostnaden för att köpa en bulkbox av en enda typ av transistor också vara lägre. Prestandan hos dina kretsar kommer att förbättras om dina logiska grindar är byggda med matchande transistorer, och projektet i sin helhet kommer att bli mer givande i slutändan.