Det finns olika typer av logikfamiljer tillgängliga som används vid design av digitala logikkretsar; Resistor Transistor Logic (RTL), Emitter Coupled Logic (ECL), Diode Transistor Logic (DTL), komplementär metalloxidhalvledarlogik (CMOS) och Transistor-Transistor Logic (TTL) . Av dessa logikfamiljer användes DTL-logikfamiljen vanligt före 1960- och 1970-talen för att ersätta mer avancerade logikfamiljer som CMOS och TTL. Diod-transistorlogik är en klass av digitala kretsar som är designad med dioder och transistorer. Så kombinationen av dioder och transistorer gör det möjligt att skapa komplexa logiska funktioner med ganska små komponenter. Den här artikeln ger kort information om DTL eller diodtransistorlogik och dess tillämpningar.

Vad är diodtransistorlogik?

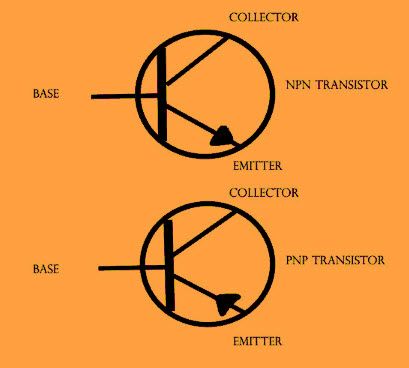

Diodtransistorlogik är en logikkrets som tillhör den digitala logikfamiljen som används för att skapa digitala kretsar. Denna krets kan designas med dioder och transistorer där dioder används på ingångssidan och transistorer används på utgångssidan, så det är känt som DTL. DTL är en specifik klass av kretsar som används i nuvarande digital elektronik för att bearbeta elektriska signaler.

I denna logiska krets är dioder användbara för att utföra logiska funktioner, medan transistorer används för att utföra förstärkningsfunktionerna. DTL har många fördelar jämfört med motstånd transistorlogik som; de högre fan-out-värdena och den höga brusmarginalen så ersätts DTL RTL-familjen. De egenskaper hos diodtransistorlogik omfattar huvudsakligen; digital kulturlös, digital strateg, digital arkitekt, organisatorisk smidigast, kundcentrerad, dataförespråkare, digital arbetsplatsdesigner & affärsprocessoptimerare.

Diod Transistor Logic Circuit

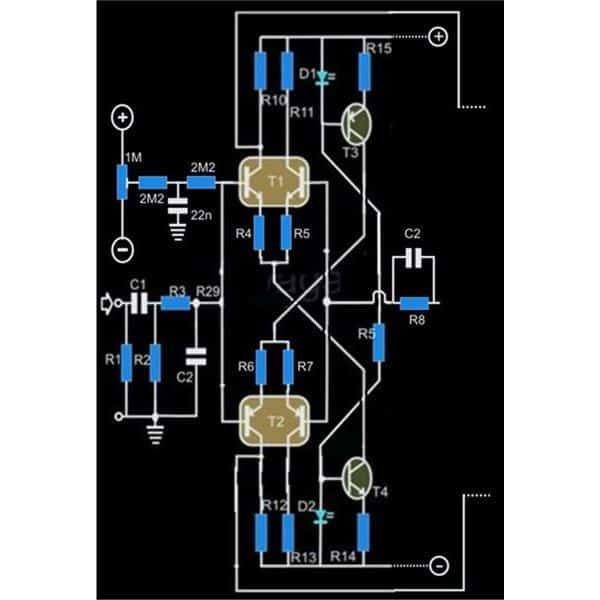

Diodtransistorns logiska krets visas nedan. Detta är en logisk NAND-grindkrets för diodtransistorer med två ingångar. Denna krets är designad med två dioder & en transistor där två dioder indikeras med D1, och D2 & motståndet indikeras med R1 som utgör ingångssidan av den logiska kretsen. Q1-transistorns CE-konfiguration & R2-motståndet utgör utgångssidan. 'C1'-kondensatorn i denna krets används för att ge en överväxlingsström under hela kopplingstiden och detta minskar kopplingstiden till någon nivå.

Diodtransistorlogik fungerar

Närhelst båda ingångarna på kretsarna A och B är LÅG, kommer både D1 och D2-dioderna att bli framåtspända, sålunda kommer dessa dioder att leda i framåtriktningen. Således kommer strömförsörjningen på grund av spänningsförsörjningen (+VCC = 5V) att leverera till GND genom hela R1-motståndet och de två dioderna. Spänningsförsörjningen blir reducerad inom R1-motståndet och det kommer inte att räcka med att slå PÅ Q1-transistorn, därför kommer Q1-transistorn att vara i avstängt läge. Så o/p vid 'Y'-terminalen kommer att vara Logic 1 eller HIGH-värde.

När någon av ingångarna är LÅG, kommer motsvarande diod att vara framåtspänd, så en liknande operation kommer att inträffa. Eftersom vilken som helst av dessa dioder är framåtspänd, kommer ström att tillföras marken genom hela den framåtspända dioden, så att 'Q1'-transistorn kommer att vara i avstängningsläge, så utgången vid 'Y'-terminalen kommer att vara hög eller logisk 1.

Närhelst båda A- och B-ingångarna är HÖG kommer båda dioderna att vara omvänt förspända, så att båda dioderna inte leder. Så i detta tillstånd kommer spänningen från +VCC-källan att vara tillräcklig för att driva Q1-transistorn till ledningsläge.

Därför leder transistorn genom emitter- och kollektorterminalerna. Hela spänningen reduceras inom 'R2'-motståndet och utgången på 'Y'-terminalen kommer att ha LÅG o/p och anses vara låg eller logisk 0.

Sanningstabell

DTL-sanningstabellen visas nedan.

|

A |

B | OCH |

|

0 |

0 | 1 |

|

0 |

1 |

1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

Diodtransistorns logiska utbredningsfördröjning är ganska stor. Närhelst alla ingångar är logiska höga kommer transistorn att gå in i mättnads- och laddningsuppbyggnader inom basområdet. När en ingång är låg bör denna laddning tas bort, vilket ändrar utbredningstiden. Att påskynda diodtransistorlogiken på ett sätt är att lägga till en kondensator över motståndet R3. Här hjälper denna kondensator till att stänga av transistorn genom att eliminera den ackumulerade laddningen vid basterminalen. Kondensatorn i denna krets hjälper också till att slå på transistorn genom att förbättra den första basdrivningen.

Modifierad diodtransistorlogik

Den modifierade DTL NAND-grinden visas nedan. Motstånds- och kondensatorkomponenternas stora värden är mycket svåra att ekonomiskt tillverka på en IC. Så följande DTL NAND-grindkrets kan modifieras för implementering av IC genom att helt enkelt eliminera C1-kondensatorn, minska värdena på motståndet och använda transistorer & dioder där det är möjligt. Denna modifierade krets använder helt enkelt en enda positiv matning och denna krets inkluderar ett ingångssteg med dioder D1 och D2, ett R3-motstånd och en OCH-grind som följs genom en transistoriserad inverterare.

Arbetssätt

Den här kretsens funktion är att den här kretsen har två ingångar A och B, och ingångsspänningar som A & B kan vara antingen HÖG eller LÅG.

Om båda ingångarna A och B är låga eller logisk 0, kommer båda dioderna att bli framåtspända, så potentialen vid 'M' är spänningsfallet för en diod som är 0,7 V. Även om för att driva 'Q'-transistorn till ledning , då behöver vi 2,1 V för att förspänna dioderna D3, D4 & BE-övergången till 'Q'-transistorn, så denna transistor är cutoff och ger utgång Y = 1

Y = Vcc = Logisk 1 och för A = B = 0, Y = 1 eller Hög.

Om någon av ingångarna, antingen A eller B är låg, kan vilken som helst av ingångarna anslutas till GND med vilken terminal som helst ansluten till +Vcc, motsvarande diod kommer att leda, och VM ≅ 0,7 V & Q transistor kommer att stängas av och ger utsignalen 'Y' = 1 eller logisk hög.

Om A = 0 & B =1 (eller) om A = 1 & B = 0, utmata Y = 1 eller HÖG.

Om två ingångar som både A & B är HÖG och både A & B är anslutna helt enkelt till + Vcc, så kommer både D1 & D2 dioderna att vara omvändsbaserade och de leder inte. D3- och D4-dioderna är framåtspända och ström vid basterminalen matas enkelt till Q-transistorn genom Rd, D3 och D4. Transistorn kan drivas till mättnad och o/p-spänningen blir en låg spänning.

För A = B = 1, utgången Y = 0 eller LÅG.

Tillämpningarna av modifierad DTL inkluderar följande.

Större fläkt ut är möjlig på grund av att efterföljande grindar har hög impedans med det logiska HIGH-tillståndet. Denna krets har överlägsen brusimmunitet. Användningen av flera dioder istället för motstånd och kondensatorer kommer att göra denna krets mycket ekonomisk inom den integrerade kretsformen.

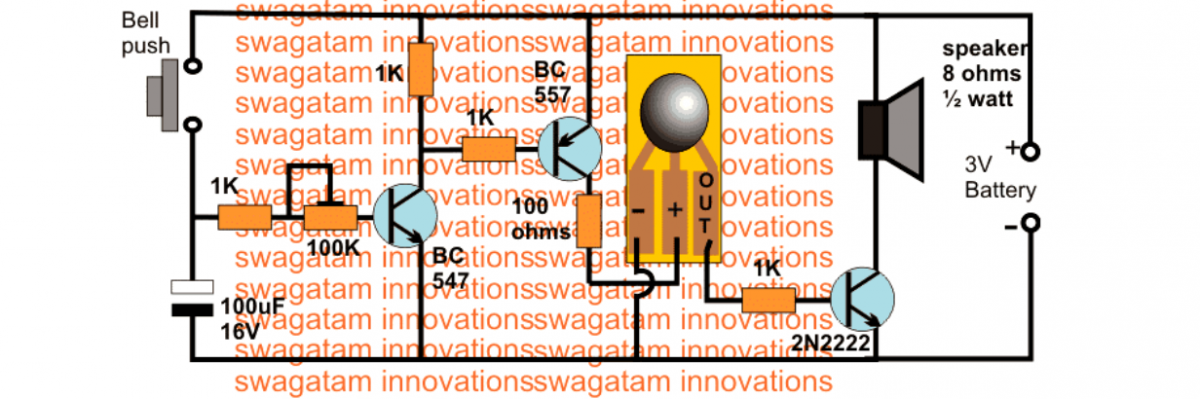

Diod Transistor Logic NOR Gate

Diodtransistorns logiska NOR-grind är utformad på liknande sätt som DTL NAND-grinden med en DRL-ELLER-grind med en transistorväxelriktare. DTL NOR-kretsar kan designas mer elegant genom att helt enkelt kombinera olika DTL-växelriktare genom en gemensam utgång. På detta sätt kan flera växelriktare förenas för att ge nödvändiga ingångar för NOR-grinden.

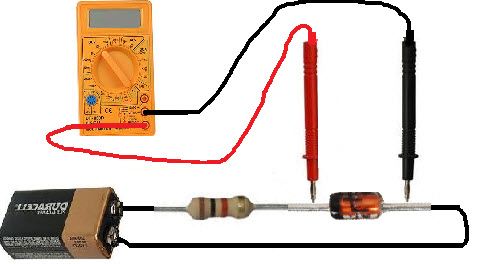

Denna krets kan utformas med komponenterna i DTL Inverter-kretsen förutom strömförsörjning & två 4,7 K motstånd , 1N914 eller 1N4148 kiseldioder. Anslut kretsen enligt kretsen som visas nedan.

Arbetssätt

När anslutningarna är gjorda måste du ge strömförsörjningen till kretsen. Efter det, applicera fyra möjliga ingångskombinationer vid A & B från strömförsörjningen med en dip-switch. Nu måste du för varje ingångskombination notera det logiska tillståndet för utgången 'Q' som representeras med LED & spela in den utgången. Jämför resultaten med NOR-grindoperationen. När du är klar med dina observationer, stäng sedan av strömförsörjningen.

|

A |

B |

Y = (A+B)' |

|

0 |

0 | 1 |

|

0 |

1 | 0 |

| 1 | 0 |

0 |

| 1 | 1 |

0 |

Diod Transistor Logik OCH Gate

Diodtransistorns logik OCH-grinden visas nedan. I denna krets, tillstånden logik som; 1 & 0 tas som +5V positiv logik & 0V motsvarande.

Närhelst någon ingång från A1, A2 (eller) A3 är i ett lågt logiskt tillstånd kommer dioden som är ansluten till den ingången att vara i framåtförspänning efter det, transistorn kommer att stängas av och utgången kommer att vara LÅG eller logisk 0 På liknande sätt, om alla tre ingångarna är på logik 1, leder ingen av dioderna och transistorn leder starkt. Efter det mättas transistorn och utgången blir HÖG eller logisk 1.

Sanningstabellen för diodtransistorlogik och gate visas nedan.

|

A1 |

A2 | A3 |

Y = A.B |

|

0 |

0 | 0 | 0 |

|

0 |

0 | 1 | 0 |

|

0 |

1 | 0 |

0 |

| 0 | 1 | 1 |

0 |

|

1 |

0 | 0 | 0 |

|

1 |

0 | 1 |

0 |

| 1 | 1 | 0 |

0 |

| 1 | 1 | 1 |

1 |

Jämförelse mellan DTL, TTL & RTL

Skillnaderna mellan DTL, TTL och RTL diskuteras nedan.

| DTL | TTL |

RTL |

| Termen DTL står för Diode-Transistor Logic. | Termen TTL står för Transistor-Transistor Logic. | Termen RTL står för Resistor-Transistor Logic. |

| I DTL är de logiska grindarna designade med PN-övergångsdioder och transistorer. | I en TTL är logiska grindar designade med BJT.

|

I RTL är de logiska grindarna designade med motstånd och transistor. |

| I DTL används dioder som i/p-komponenter och transistorer som o/p-komponenter. | I TTL används en transistor för förstärkning medan en annan transistor används för omkopplingsändamål. | Motståndet i RTL används som i/p-komponenten och transistorn används som o/p-komponenten |

| DTL-svaret är bättre jämfört med RTL. | TTL-svaret är mycket bättre än DTL och RTL. | RTL-svaret är långsamt. |

| Strömförlusten är låg. | Den har mycket låg effektförlust. | Effektförlusten är hög. |

| Dess konstruktion är komplex. | Dess konstruktion är mycket enkel. | Dess konstruktion är enkel. |

| DTL minsta fanout är 8. | Minsta TTL fanout är 10. | RTL minsta fanout är 5. |

| Effektförlusten för varje gate är vanligtvis 8 till 12 mW. | Effektförlusten för varje gate är vanligtvis 12 till 22 mW. | Effektförlusten för varje gate är vanligtvis 12 mW. |

| Dess bullerimmunitet är bra. | Dess bullerimmunitet är mycket bra. | Dess brusimmunitet är medelhög. |

| Dess typiska utbredningsfördröjning för grinden är 30 ns. | Dess typiska utbredningsfördröjning för grinden är 12 till 6 ns. | Dess typiska utbredningsfördröjning för grinden är 12 ns. |

| Dess klockfrekvens är 12 till 30 MHz. | Dess klockfrekvens är 15 till 60 MHz. | Dess klockfrekvens är 8 MHz. |

| Den har ett ganska stort antal funktioner. | Den har ett mycket stort antal funktioner. | Den har ett stort antal funktioner. |

| DTL-logik används i grundläggande omkopplings- och digitala kretsar. | TTL-logik används i moderna digitala kretsar och integrerade kretsar. | RTL används inom gamla datorer. |

Fördelar

Fördelarna med en diodtransistorlogikkrets inkluderar följande.

- Omkopplingshastigheten för DTL är snabbare jämfört med RTL.

- Användningen av dioder inom DTL-kretsar gör dem billigare eftersom tillverkningen av dioder på IC:er är enklare jämfört med motstånd och kondensatorer.

- Strömförlusten inom DTL-kretsar är mycket låg.

- DTL-kretsar har snabbare kopplingshastigheter.

- DTL har större fan-out och förbättrad brusmarginal.

De nackdelar med diodtransistorlogikkretsar inkluderar följande.

- DTL har en låg driftshastighet jämfört med TTL.

- Den har en extremt stor gate-utbredningsfördröjning.

- För hög ingång går utsignalen från DTL till mättnad.

- Den genererar värme under hela operationen.

Ansökningar

De tillämpningar av diodtransistorlogik inkluderar följande.

- Diod-Transistor Logic används för att designa och tillverka digitala kretsar där logiska grindar använd dioder inom ingångssteget & BJTs i slutsteget.

- DTL är en specifik typ av krets som används i nuvarande digital elektronik för att bearbeta elektriska signaler.

- DTL används för att göra enkla logiska kretsar.

Detta är alltså en översikt över diodtransistorlogik , krets, funktion, fördelar, nackdelar och tillämpningar. DTL-kretsar är mer komplexa jämfört med RTL-kretsar, men denna logik har förändrat RTL på grund av dess överlägsna FAN OUT-kapacitet och förbättrade brusmarginal men DTL har en långsam hastighet. Här är en fråga till dig, vad är RTL?