Uttrycket CMOS står för 'Complementary Metal Oxide Semiconductor'. Detta är en av de mest populära teknikerna inom designindustrin för datachip och används idag allmänt för att bildas integrerade kretsar i många och varierade applikationer. Dagens datorminnen, processorer och mobiltelefoner använder sig av denna teknik på grund av flera viktiga fördelar. Denna teknik använder både P-kanal och N-kanal halvledare. En av de mest populära MOSFET-teknikerna som finns idag är kompletterande MOS- eller CMOS-teknik. Detta är den dominerande halvledarteknologin för mikroprocessorer, mikrokontrollerchips, minnen som RAM, ROM, EEPROM och applikationsspecifika integrerade kretsar (ASIC).

Introduktion till MOS-teknik

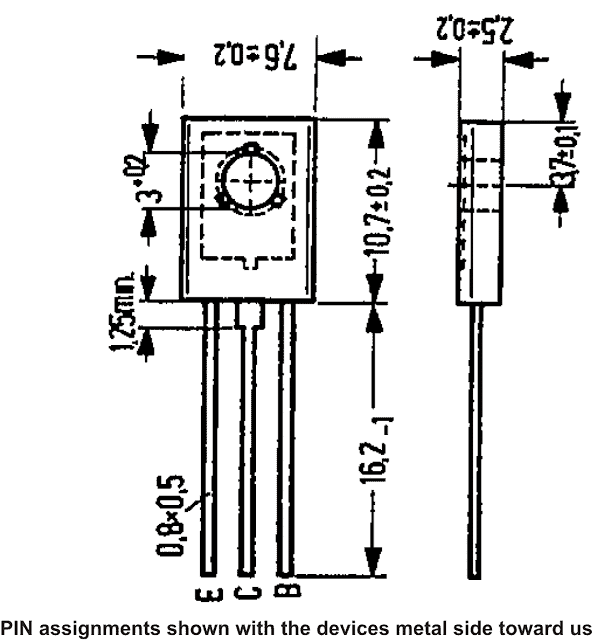

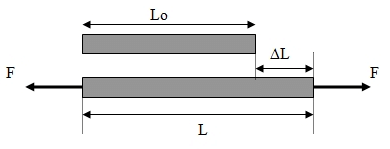

I IC-designen är transistorn den grundläggande och viktigaste komponenten. Så MOSFET är en typ av transistor som används i många applikationer. Bildandet av denna transistor kan göras som en sandwich genom att inkludera ett halvledarskikt, i allmänhet en skiva, en skiva från en enda kristall av kisel, ett lager av kiseldioxid och ett metallskikt. Dessa lager möjliggör att transistorerna kan bildas i halvledarmaterialet. En bra isolator som Sio2 har ett tunt lager med tjocklek på hundra molekyler.

Transistorerna som vi använder polykristallint kisel (poly) istället för metall för deras grindpartier. Polysilicon-grinden i FET kan bytas ut nästan med metallgrindar i storskaliga IC. Ibland kallas både polysilikon och metall-FET: er för IGFET, vilket betyder isolerade grind-FET: er, eftersom Sio2 nedanför grinden är en isolator.

CMOS (komplementär metalloxid halvledare)

Den huvudsakliga fördelen med CMOS framför NMOS och BIPOLAR-tekniken är den mycket mindre strömavledningen. Till skillnad från NMOS- eller BIPOLAR-kretsar har en kompletterande MOS-krets nästan ingen statisk strömförlust. Strömmen försvinner bara om kretsen faktiskt växlar. Detta gör det möjligt att integrera fler CMOS-grindar på en IC än i NMOS eller bipolär teknik vilket resulterar i mycket bättre prestanda. Kompletterande metalloxid halvledartransistor består av P-kanal MOS (PMOS) och N-kanal MOS (NMOS). Se länken om du vill veta mer om tillverkningsprocessen för CMOS-transistorn .

CMOS (komplementär metalloxid halvledare)

NMOS

NMOS är byggt på ett p-typ substrat med n-typ källa och avlopp diffunderat på det. I NMOS är majoriteten av bärare elektroner. När en hög spänning appliceras på grinden kommer NMOS att leda. På samma sätt, när en låg spänning appliceras på grinden, kommer NMOS inte att leda. NMOS anses vara snabbare än PMOS, eftersom bärarna i NMOS, som är elektroner, färdas dubbelt så snabbt som hålen.

NMOS Transistor

PMOS

P-kanal MOSFET består av P-typ källa och avlopp diffunderat på ett N-typ substrat. De flesta bärare är hål. När en hög spänning appliceras på grinden kommer PMOS inte att leda. När en låg spänning appliceras på grinden kommer PMOS att leda. PMOS-enheterna är mer immuna mot brus än NMOS-enheter.

PMOS-transistor

CMOS arbetsprincip

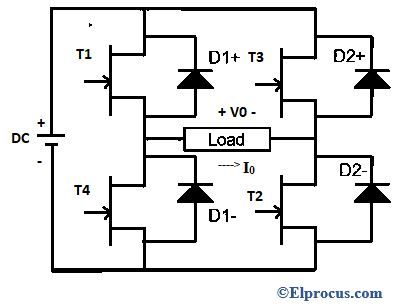

I CMOS-teknik används både N-typ och P-typ transistorer för att utforma logiska funktioner. Samma signal som slår på en transistor av en typ används för att stänga av en transistor av den andra typen. Denna egenskap möjliggör design av logiska enheter med endast enkla omkopplare utan behov av ett uppdragningsmotstånd.

I CMOS logiska grindar en samling av MOSFET-n-typ är anordnad i ett neddragningsnät mellan utgången och lågspänningsförsörjningsskenan (Vss eller ganska ofta jordad). Istället för lastmotståndet för NMOS-logikgrindar har CMOS-logikgrindar en samling av P-typ MOSFET i ett uppdragningsnätverk mellan utgången och högspänningsskenan (ofta kallad Vdd).

CMOS med Pull Up & Pull Down

Således, om både en p-typ och en n-typ transistor har sina grindar anslutna till samma ingång, kommer p-typ MOSFET att vara PÅ när n-typ MOSFET är AV, och vice versa. Nätverken är ordnade så att det ena är PÅ och det andra AV för alla ingångsmönster som visas i figuren nedan.

CMOS erbjuder relativt hög hastighet, låg effektförlust, höga brusmarginaler i båda tillstånden och kommer att fungera över ett stort antal käll- och ingångsspänningar (förutsatt att källspänningen är fast). Dessutom, för en bättre förståelse av den kompletterande arbetsmetoden för metalloxidhalvledare, måste vi kortfattat diskutera CMOS-logikgrindar som förklaras nedan.

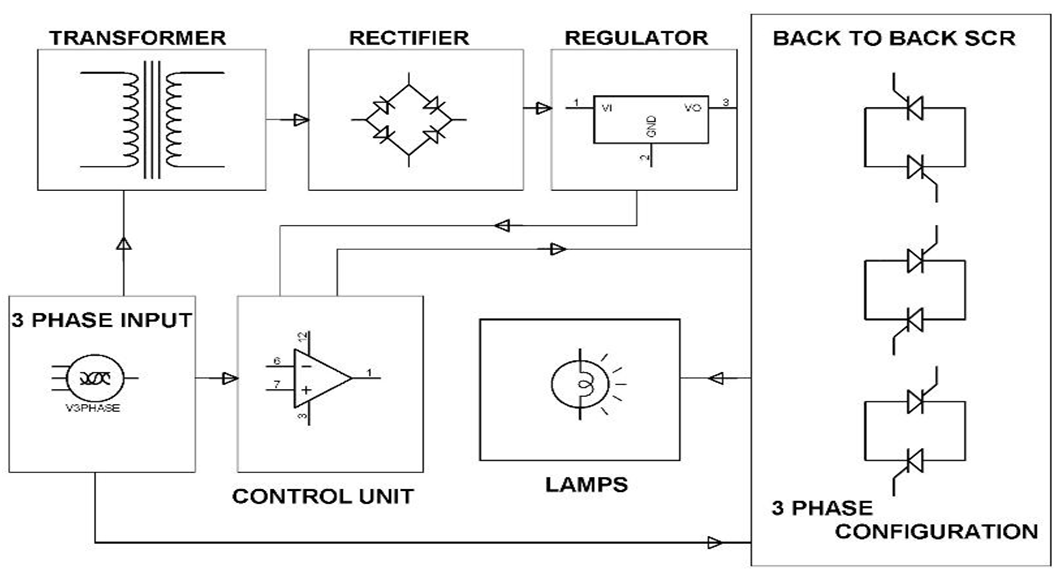

Vilka enheter använder CMOS?

Teknik som CMOS används i olika chips som mikrokontroller, mikroprocessorer, SRAM (statisk RAM) och andra digitala logikkretsar. Denna teknik används i ett brett spektrum av analoga kretsar som inkluderar dataomvandlare, bildsensorer och högt integrerade sändtagare för flera typer av kommunikation.

CMOS-inverterare

Växelriktarkretsen enligt bilden nedan. Den består av PMOS och NMOS FET . Ingången A fungerar som grindspänning för båda transistorerna.

NMOS-transistorn har ingång från Vss (jord) och PMOS-transistorn har ingång från Vdd. Terminalen Y matas ut. När en hög spänning (~ Vdd) ges vid ingångsanslutningen (A) på växelriktaren blir PMOS en öppen krets och NMOS stängs AV så att utgången dras ner till Vss.

CMOS-inverterare

När en lågnivåspänning ( Figuren nedan visar en kompletterande MOS NAND-grind med 2 ingångar. Den består av två serier NMOS-transistorer mellan Y och Ground och två parallella PMOS-transistorer mellan Y och VDD. Om antingen ingång A eller B är logisk 0 kommer åtminstone en av NMOS-transistorerna att vara FRÅN och bryta vägen från Y till mark. Men åtminstone en av pMOS-transistorerna är PÅ, vilket skapar en väg från Y till VDD. Två ingångar NAND Gate Följaktligen kommer utgången Y att vara hög. Om båda ingångarna är höga kommer båda nMOS-transistorerna att vara PÅ och båda pMOS-transistorerna kommer att vara AV. Därför kommer produktionen att vara logisk låg. Sanningstabellen för NAND-logikgrinden i tabellen nedan. En NOR-grind med 2 ingångar visas i figuren nedan. NMOS-transistorerna är parallella för att dra utgången lågt när någon av ingångarna är hög. PMOS-transistorerna är i serie för att dra utgången högt när båda ingångarna är låga, enligt nedanstående tabell. Resultatet lämnas aldrig flytande. Två ingångar NOR Gate Sanningstabellen för NOR-logikgrinden i tabellen nedan. Tillverkningen av CMOS-transistorer kan göras på kiselskivan. Skivans diameter varierar från 20 mm till 300 mm. I detta är litografiprocessen densamma som tryckpressen. På varje steg kan olika material deponeras, etsas på annat sätt i mönster. Denna process är mycket enkel att förstå genom att se rånens topp såväl som tvärsnitt inom en förenklad monteringsmetod. Tillverkningen av CMOS kan åstadkommas genom att använda tre tekniker, nämligen N-well pt P-well, Twin well, en SOI (Silicon on Insulator). Se den här länken för att veta mer om CMOS-tillverkning . Den typiska livslängden för ett CMOS-batteri är ungefär 10 år. Men detta kan förändras baserat på användningen och omgivningen varhelst datorn bor. När CMOS-batteriet misslyckas kan datorn inte behålla exakt tid och datum på datorn när den stängts av. Till exempel, när datorn är PÅ kan du se tid och datum som 12:00 PM & 1 januari 1990. Detta fel anger att batteriet i CMOS misslyckades. De viktigaste egenskaperna hos CMOS är låg statisk strömanvändning, enorm ljudimmunitet. När den enskilda transistorn från MOSFET-transistorparet är avstängd använder seriekombinationen betydande kraft under hela omkopplingen bland de två som anges som ON & OFF. Som ett resultat genererar dessa enheter inte spillvärme jämfört med andra typer av logiska kretsar som TTL eller NMOS-logik, som vanligtvis använder viss ständig ström även om de inte ändrar tillstånd. Dessa CMOS-egenskaper möjliggör integrering av logiska funktioner med hög densitet i en integrerad krets. På grund av detta har CMOS blivit den mest använda tekniken som ska köras inom VLSI-marker. Frasen MOS är en hänvisning till MOSFET: s fysiska struktur som inkluderar en elektrod med en metallgrind som är placerad på toppen av en oxidisolator av halvledarmaterial. Ett material som aluminium används bara en gång men materialet är nu polykisel. Utformningen av andra metallgrindar kan göras med hjälp av en comeback genom ankomsten av hög-k dielektriska material inom processen för CMOS-processen. Bildsensorerna som laddningskopplad enhet (CCD) och kompletterande metalloxid-halvledare (CMOS) är två olika typer av tekniker. Dessa används för att fånga bilden digitalt. Varje bildsensor har sina fördelar, nackdelar och applikationer. Huvudskillnaden mellan CCD och CMOS är sättet att fånga ramen. En laddningskopplad enhet som CCD använder en global slutare medan CMOS använder en rullande slutare. Dessa två bildsensorer ändrar laddningen från ljus till elektrisk och bearbetar den till elektroniska signaler. Tillverkningsprocessen som används i CCD: er är speciell för att bilda förmågan att flytta laddningen över IC utan förändring. Så denna tillverkningsprocess kan leda till sensorer av extremt hög kvalitet om ljuskänslighet och trohet. Däremot använder CMOS-chips fasta tillverkningsprocedurer för att designa chipet och en liknande process kan också användas vid tillverkning av mikroprocessorer. På grund av skillnaderna i tillverkning finns det några tydliga skillnader mellan sensorerna som CCD 7 CMOS. CCD-sensorer kommer att fånga bilder med mindre brus och enorm kvalitet medan CMOS-sensorer vanligtvis är mer benägna att bullra. Vanligtvis använder CMOS mindre ström medan CCD använder mycket ström som mer än 100 gånger för CMOS-sensorn. Tillverkningen av CMOS-chips kan göras på vilken typisk Si-produktionslinje som helst eftersom de tenderar att vara mycket billiga jämfört med CCD-enheter. CCD-sensorer är mer mogna eftersom de massproduceras under en lång period. Både CMOS- och CCD-bilderna beror på effekten av fotoelektrisk för att avge den elektriska signalen från ljuset Baserat på ovanstående skillnader används CCD i kameror för att rikta in bilder av hög kvalitet genom massor av pixlar och enastående ljuskänslighet. Vanligtvis har CMOS-sensorer mindre upplösning, kvalitet och känslighet. En låsning kan definieras som när kortslutningen inträffar mellan de två terminalerna som ström och jord så att hög ström kan genereras och IC kan skadas. I CMOS är latch-up förekomsten av lågimpedansspår bland power rail & markskenan på grund av kommunikationen mellan de två transistorerna som parasitisk PNP och NPN transistorer . I CMOS-kretsen är de två transistorerna som PNP & NPN anslutna till två matningsskenor som VDD & GND. Skyddet av dessa transistorer kan göras genom motstånd. I en spärröverföring kommer strömmen att flyta från VDD till GND rakt igenom de två transistorerna så att en kortslutning kan uppstå, varför extrem ström kommer att strömma från VDD till markterminalen. Det finns olika metoder för att förhindra låsning Vid spärrförebyggande kan högt motstånd placeras i spåret för att stoppa flödet av ström genom hela försörjningen och för att göra β1 * β2 under 1 genom att använda följande metoder. Strukturen hos parasitisk SCR kommer att vara näbbad i omgivningen av transistorer som PMOS och NMOS genom ett isolerande oxidskikt. Tekniken för spärrskydd kommer att stänga av enheten när spärrning upptäcks. Testtjänsterna för låsning kan utföras av många leverantörer på marknaden. Detta test kan göras genom en sekvens av försök att aktivera SCR-strukturen i CMOS IC medan de relaterade stiften kontrolleras när överström flyter genom den. Det rekommenderas att få de första proverna från det experimentella partiet och skicka dem till ett testlaboratorium för Latch-up. Detta laboratorium kommer att tillämpa den största möjliga strömförsörjningen och ge sedan strömförsörjningen till chipets ingångar och utgångar när en Latch-up sker genom övervakning av strömförsörjningen. Fördelarna med CMOS inkluderar följande. De viktigaste fördelarna med CMOS jämfört med TTL är bra brusmarginal samt mindre strömförbrukning. Detta beror på ingen rak ledning från VDD till GND, falltider baserat på ingångsförhållandena, då kommer överföringen av den digitala signalen att bli enkel och låg kostnad genom CMOS-chips. CMOS används för att förklara mängden minne på datorns moderkort som kommer att lagras i BIOS-inställningarna. Dessa inställningar inkluderar främst datum, tid och inställningar för hårdvara Utgångarna om CMOS kör aktivt på båda sätten Nackdelarna med CMOS inkluderar följande. Kompletterande MOS-processer implementerades i stor utsträckning och har i grunden ersatt NMOS och bipolära processer för nästan alla digitala logikapplikationer. CMOS-teknik har använts för följande digitala IC-design. Således är den CMOS-transistorn är mycket känd eftersom de använder elkraft effektivt. De använder inte elförsörjningen när de ändras från ett tillstånd till ett annat. Dessutom fungerar de gratis halvledarna ömsesidigt för att stoppa o / p-spänningen. Resultatet är en lågeffektsdesign som ger mindre värme, på grund av detta har dessa transistorer ändrat andra tidigare konstruktioner som CCD-enheter inom kamerasensorer och används i de flesta av de nuvarande processorerna. CMOS-minnet i en dator är ett slags icke-flyktigt RAM-minne som lagrar BIOS-inställningar och information om tid och datum. Jag tror att du har fått en bättre förståelse för detta koncept. Dessutom är alla frågor angående detta koncept eller elektronikprojekt , ge dina värdefulla förslag genom att kommentera i kommentarfältet nedan. Här är en fråga till dig, varför CMOS är att föredra framför NMOS? INMATNING LOGIKINGÅNG PRODUKTION LOGIKUTGÅNG 0 v 0 Vdd 1 Vdd 1 0 v 0 CMOS NAND-grind

TILL B Neddragningsnätverk Pull-up-nätverk UTGÅNG Y 0 0 AV PÅ 1 0 1 AV PÅ 1 1 0 AV PÅ 1 1 1 PÅ AV 0 CMOS NOR-porten

TILL B Y 0 0 1 0 1 0 1 0 0 1 1 0 CMOS-tillverkning

En livstid för CMOS-batteri

Felsymptom på CMOS-batteri

CMOS-egenskaper

CCD mot CMOS

I vissa applikationer har CMOS-sensorer nyligen förbättrats till den punkt där de når nära likhet med CCD-enheter. Generellt är CMOS-kameror inte dyra och de har en hög batteritid.Latch-Up i CMOS

Fördelar

TTL är en digital logisk krets där bipolära transistorer arbetar på DC-pulser. Flera transistorlogiska grindar består normalt av en enda IC.Nackdelar

CMOS-applikationer