Inlägget diskuterar pinout-funktionen och andra viktiga specifikationer för IC 4043. Låt oss lära oss mer om det fullständiga databladet för detta mycket intressanta chip.

Pinout-datablad för IC 4043

Tekniskt sett är IC 4043 en quad set / reset (R / S) spärr med 3 logiska tillståndsutgångar.

För att vara mer exakt har detta chip 4 uppsättningar ingångar (vilket betyder 8 ingångsuttag) och 4 motsvarande enstaka utgångar.

De fyra uppsättningarna ingångar består av 4 par inställnings- / återställningsingångar.

För varje uppsättning / återställning har vi en motsvarande utgång.

Alla dessa inställda återställningsingångar svarar på höga logiska signaler, vilket skapar en bistabil effekt vid deras motsvarande utgångsuttag.

Bistabil Flip / Flop

Bistable hänvisar till flip-flop-handling, med andra ord, en hög puls till 'set' -ingången gör motsvarande utgång hög från sitt ursprungliga låga tillstånd, och en hög till återställningsingången återställer ovanstående tillstånd från högt tillbaka till lågt tillstånd.

För att göra motsvarande utgångar höga måste vi därför tillämpa en hög på deras 'inställda' ingångar och för att göra utgångarna låga igen behöver vi helt enkelt använda en annan hög på deras återställningsingångar.

Funktionen för in- och utgångsuttag är så enkel som det.

Utöver detta har IC en annan intressant ingång pinout OE som är en gemensam utgång möjliggör pinout.

Ställ in / återställ funktion

För att möjliggöra ovanstående förklarade inställnings- / återställningsåtgärder i IC: n bör denna OE-ingång anslutas med logik hög eller helt enkelt med Vdd (matningsröst).

I ovanstående situation är utdata tillåtet med den angivna flip-flop-funktionen.

Om OE-ingången är ansluten till jord, fryser utgången och producerar ett högimpedanssvar, som varken visar en låg utgång eller en hög, snarare låser ingången ett icke-svarande blockerat tillstånd, därav namnet 3 logisk tillståndsutgång.

Således kan OE-ingången användas för att stänga av IC-funktionen om det behövs för en viss applikation.

IC fungerar bäst med matningsspänningar från 5 till 15V.

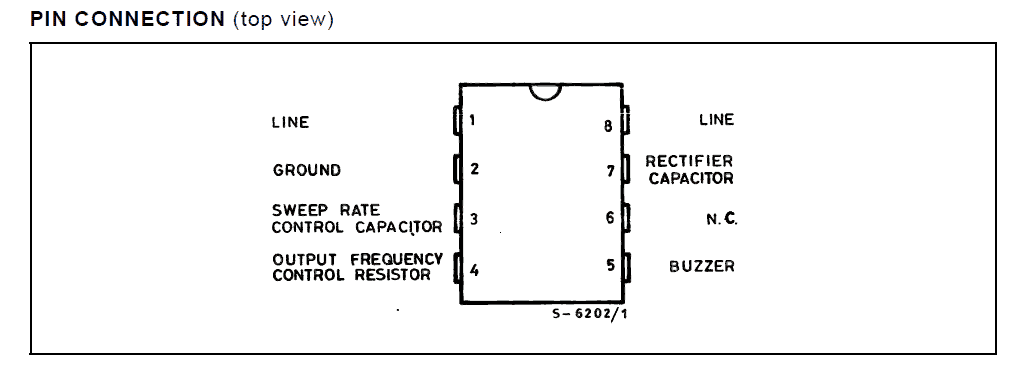

Låt oss sammanfatta ingångsutgångens pinout-funktioner och specifikationer för IC 4043 med följande data:

- 1Q till 4Q (Pins: 2, 9, 10, 1) 3-tillstånds buffrad spärrutgång

- 1R till 4R (Pins: 3, 7, 11, 15) återställningsingång (aktiv HÖG)

- 1S till 4S (Pins: 4, 6, 12, 14) ställa in ingång (aktiv HÖG)

- OE (Pin: 5) gemensam ingång för aktivering av utgång

- VSS (stift: 8) jordförsörjningsspänning

- N.C. (stift: 13) inte ansluten

- VDD (stift: 16) matningsspänning

Fler uppdateringar:

I dessa inlägg försöker vi förstå hur IC 4043 och IC 4044 fungerar genom att studera de olika specifikationerna, databladet för enheterna och deras pinout-arrangemang.

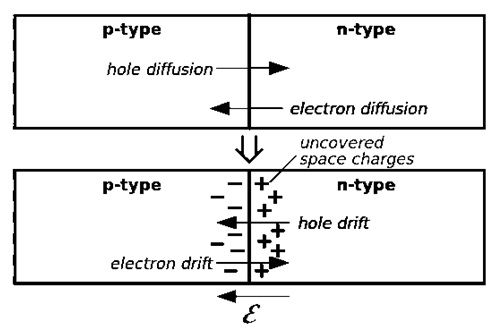

I grund och botten är båda varianterna fyrkorsade CMOS 3-state R / S eller Reset / Set Latches. Quad betyder att ha 4 utgångar som kan ställas in eller spärras med en logik hög genom en styringångssignal, eller återställas till logisk noll genom en efterföljande insignal.

Med 3-tillståndsfunktionen kan IC: n styras med 3-logik

Den grundläggande arbetsprincipen för IC 4043 och IC 4044 är densamma som ovan, den enda skillnaden är att IC 4043B är fyrkorsade 3-tillstånd INTE HELLER Spärr och IC 4044B är fyrkors-kopplade 3-tillstånd NAND Spärr.

Pinout-diagram

Följande pinouts-diagram över IC: erna visar enheternas interna struktur och pinout-detaljer:

I diagrammen ovan kan vi se att var och en av typerna har 4 spärrar med en utgång och 2 individuella RESET / SET-ingångar. Funktionen för ENABLE-stiftet för alla SET / RESET-ingångarna är identisk.

En logik HÖG vid ENABLE-stiftet gör att spärrtillstånden kan anslutas till relevanta utgångar, en logisk låg eller 0 kopplar bort spärrtillstånden från deras utgångar vilket orsakar en fullständig öppen krets över utgångarna.

NOR Latch, NAND Latch Equivalent Logic Diagram

Följande diagram visar motsvarande spärrar i form av NOR- och NAND-spärrar, som finns inuti var och en av de fyra spärrarna för de enskilda IC-enheterna.

Som vi kan se styrs var och en av spärrblocken med 3 logiska kontrollingångar, nämligen SET, RESET och ENABLE, därför är utgången beroende av dessa 3 ingångstillstånd. Sanningstabellen för dessa tre logiska tillstånd kan läsas från följande diagram:

I ovanstående sanningstabell kan hela formen för de olika förkortade symboliska alfabeten förstås som ges nedan: S = SET Pin R = RESET Pin E = ENABLE Pin Q = OUTPUT Pin OC = Open Circuit NC = No Change

Huvudfunktionerna i IC 4043 och IC 4044 sammanfattas nedan:

Praktisk grundläggande arbetssimulering av SET / RESET och ENABLE Pins

Arbetsbeskrivning

Från ovanstående simulerings-GIF kan vi förstå hur fyrspärrmodulerna fungerar med följande punkter:

När SET appliceras med en positiv matning går utgången högt och låses även om den positiva potentialen tas bort från SET-stiftet, vilket indikeras av den röda lysdioden (framåtförspänd).

När RESET-stiftet appliceras med en positiv puls bryts spärren och utgången går permanent LÅG även om det positiva tas bort från RESET-stiftet. Detta indikeras av belysningen av den blå lysdioden.

Ovanstående operationer kan endast implementeras så länge IC: n ENABLE-stift har en positiv leveranspotential. När den är ansluten till en negativ eller jordpotential blir utgången från spärren öppen och svarar inte på SET / RESET-operationerna.

Tidigare: Week Day Programmable Timer Circuit Nästa: IC 4033 Pinouts, datablad, applikation