ECL (emitter coupled logic) uppfanns först hos IBM i augusti 1956 av Hannon S. Yourke. Denna logik är också känd som strömlägeslogik, som används i datorerna i IBM 7090 och 7094. ECL-familjen är mycket snabb jämfört med digital logik familjer. I allmänhet ger denna logikfamilj en fortplantningsfördröjning på mindre än 1 ns. Det är en logikfamilj baserad på bipolära kopplingstransistorer. Det är den snabbaste logiska familjekretsen som är tillgänglig för att designa ett konventionellt logiksystem. Den här artikeln diskuterar en översikt av en emitterkopplad logikkrets , arbetar med applikationer.

Vad är emitterkopplad logik?

Emitterkopplad logik är bäst BJT -baserad logikfamilj som används i den konventionella logiksystemdesignen. Ibland kallas det också för strömlägeslogik som är en digital teknik med mycket hög hastighet. Generellt anses ECL som den snabbaste logiska IC där den uppnår sin höghastighetsdrift genom att använda en mycket liten spänningssvängning och även undvika att transistorerna kommer in i mättnadsområdet.

En implementering av ECL använder en positiv matningsspänning som är känd som PECL eller positiv referens ECL. I tidiga ECL-grindar används en negativ spänningsmatning på grund av brusimmuniteten. Efter det blev positiv-referens ECL mycket berömd på grund av dess mer kompatibla logiknivåer jämfört med TTL-logikfamiljer.

Emitterkopplad logik avleder en enorm mängd statisk effekt, men dess totala strömförbrukning är låg jämfört med CMOS vid höga frekvenser. Så ECL är främst fördelaktigt i klockdistributionskretsar och högfrekvensbaserade applikationer.

Emitter Coupled Logic Features

Funktionerna hos ECL kommer att göra dem använda i många högpresterande applikationer.

- ECL tillhandahåller två utgångar som alltid är komplement till varandra eftersom driften av kretsen är baserad på en differentialförstärkare.

- Denna logikfamilj är huvudsakligen lämplig för monolitiska tillverkningsmetoder eftersom logiska nivåer är en funktion av resistorförhållanden.

- Enheterna i ECL-familjen genererar den rätta och kompletterande utgången för den föreslagna funktionen utan att använda några externa växelriktare. Följaktligen minskar det paketantalet och kraftkraven och minskar även problem som uppstår på grund av tidsfördröjningar.

- ECL-enheter i differentialförstärkardesign erbjuder bred prestandaflexibilitet, så ECL-kretsar gör det möjligt att använda både som digitala och linjära kretsar.

- Utformningen av ECL-grinden har normalt hög och låg ingångsimpedans, vilket är extremt gynnsamt för att uppnå stor fan-out såväl som drivkapacitet.

- ECL-enheter genererar en konstant strömförbrukning på strömförsörjningen för att förenkla designen av strömförsörjningen.

- Enheterna i ECL inklusive öppna emitterutgångar tillåter dem helt enkelt att inkludera transmissionsledningsdrivkapacitet.

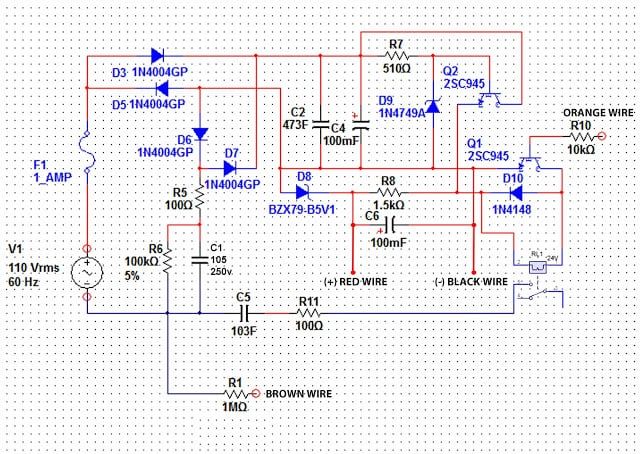

Emitterkopplad logisk krets

Den emitterkopplade logikkretsen för växelriktaren visas nedan som är utformad med resistorer och transistorer. I denna krets är emitterklämmorna på två transistorer helt enkelt anslutna till strömbegränsningsresistansen RE som används för att undvika att transistorn övergår i mättnad. Här tas transistorns utgång från kollektorterminalen istället för emitterterminalen. Denna krets ger två utgångar Vout (inverterande utgång) och Vout2 (icke-inverterande utgång) och ingångsterminalen som Vin där hög eller låg ingång ges. +Vcc = 5V.

Hur fungerar emitterkopplad logik?

Funktionen för emitterkopplad logik är att närhelst HIGH-ingången ges till ECL-kretsen, kommer den att göra 'Q1'-transistorn PÅ och Q2-transistorn AV men Q1-transistorn är inte mättad. Så detta kommer att dra VOUT2-utgången till HÖG och värdet på VOUT1-utgången kommer att vara LÅG på grund av fallet inom R1.

På liknande sätt, när VIN-värdet som ges till ECL är LÅG, kommer det att göra Q1-transistorn AV & Q2-transistorn PÅ. Så Q2-transistorn kommer inte att övergå till mättnad. Så det kommer att göra att VOUT1-utgången dras HÖGT värde och VOUT2-utgångsvärdet kommer att vara lågt på grund av fallet inom R2-motståndet.

Låt se hur transistorn Q1 och Q2 slås på och av när en spänning appliceras.

De två transistorerna som Q1 & Q2 i denna krets är anslutna som en differentialförstärkare med ett gemensamt emittermotstånd.

Spänningsförsörjningen för denna exempelkrets är VCC = 5,0, VBB = 4,0 & VEE = 0 V. Ingångsvärdena för HÖG & LÅG nivå definieras helt enkelt till 4,4 V & 3,6 V. Egentligen genererar denna krets LÅG uteffekt & HÖGA nivåer som är 0,6 volt högre; detta korrigeras dock inom riktiga ECL-kretsar.

När Vin är HÖG slås Q1-transistorn på, men inte mättad och Q2-transistorn stängs av. Så, utspänning som VOUT2 dras till 5 V genom R2-motståndet och det kan visas att spänningsfallet över R1-motståndet är cirka 0,8 V så att VOUT1 = 4,2 V (LOW). Dessutom VE = VOUT1 – VQ1 => 4,2V – 0,4V = 3,8V eftersom transistorn Q1 slås PÅ helt.

När Vin är LÅG kommer Q2-transistorn att slås på, men inte mättad och Q1-transistorn stängs AV. Därför dras VOUT1 till 5,0 V med hjälp av ett R1-motstånd & det kan visas att VOUT2 är 4,2 V. Även VE => VOUT2 – VQ2 => 4,2V – 0,8V => 3,4V när transistor Q2 slås PÅ.

I ECL är de två transistorerna aldrig i mättnad som t Ingångs-/utgångsspänningssvängningarna är ganska små som 0,8V och ingångsimpedansen är hög och utgångsresistansen är låg. Detta hjälper ECL att fungera snabbare med en mindre fördröjningstid.

Två ingångssändare kopplad logisk ELLER/NOR grindkrets

De två ingångarna emitterkopplade logiska ELLER/NOR-grindkretsen visas nedan. Denna krets är designad genom att modifiera ovanstående växelriktarkrets. Modifieringen är genom att lägga till en extra transistor på ingångssidan.

Funktionen av denna krets är mycket enkel. När ingångarna som appliceras på både Q1 och Q2 transistorerna är låga kommer utgång1 (Vout1) till ett HÖGT värde. Så denna Vout1 motsvarar utgången från NOR-grinden.

Samtidigt, om Q3-transistorn slås PÅ, kommer den att göra den andra utgången (Vout2) till HÖG. Så denna Vou2-utgång motsvarar OR-grindens utgång.

På samma sätt, om både Q1 & Q2 transistoringångarna är HÖG, kommer den att slå på Q1 & Q2 transistorerna och ge den låga utgången vid VOUT1 terminalen.

Om Q3-transistorn är avstängd under denna operation kommer den att ge hög utsignal vid VOUT2-uttaget. Så, sanningstabellen för OR/NOR gate ges nedan.

|

Ingångar |

Ingångar | ELLER |

INTE HELLER |

|

A |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Emitterkopplade logiska egenskaper

Egenskaperna för ECL inkluderar följande.

- Jämfört med TTL har ECL en snabbare fortplantningstid som sträcker sig från 0,5 till 2 ns. Men emitterkopplad logisk effektförlust är högre jämfört med TTL som 30 mW.

- I/O-spänningarna för ECL har ett litet sväng som 0,8.

- Ingångsimpedansen för ECL är hög & utgångsresistansen är låg; följaktligen ändrar transistorn sina tillstånd mycket snabbt.

- ECL:s fläktkapacitet är hög och grindfördröjningar är låga.

- O/p-logiken för ECL ändras från ett LÅG till ett HÖG tillstånd men spänningsnivåerna för dessa tillstånd kommer att variera mellan TTL och EC.

- Brusimmuniteten för ECL är 0,4V.

Fördelar och nackdelar

De fördelarna med emitterkopplad logik diskuteras nedan.

- Fanouten för ECL är 25 vilket är bättre jämfört med TTL och det är lågt jämfört med CMOS.

- Den genomsnittliga utbredningsfördröjningstiden för ECL är 1 till 4 ns vilket är bättre jämfört med både CMOS och

- TTL. Därför kallas den snabbaste logikfamiljen.

- När BJT i sändaren kopplade logiska grindar arbetar i den aktiva regionen, då har de den maximala hastigheten jämfört med alla logikfamiljer.

- ECL-grindar genererar komplementära utgångar.

- Strömbrytarspikar finns inte i strömförsörjningsledningarna.

- Utgångar kan kopplas gemensamt för att tillhandahålla den trådbundna ELLER-funktionen.

- Parametrarna för ECL förändras inte mycket genom temperaturen.

- Nejet. av funktioner som är tillgängliga från ett enda chip är hög.

De nackdelar med emitterkopplad logik diskuteras nedan.

- Den har en extremt mindre brusmarginal, dvs ±200 mV.

- Effektförlusten är hög jämfört med andra logiska grindar.

- För att samverka med andra logikfamiljer är nivåskiftare nödvändiga.

- Fanout begränsar kapacitiv belastning.

- Jämfört med TTL , ECL-grindar är dyra.

- Jämfört med CMOS & TTL är ECL-brusimmuniteten värst.

Ansökningar

Tillämpningarna av emitterkopplad logik inkluderar följande.

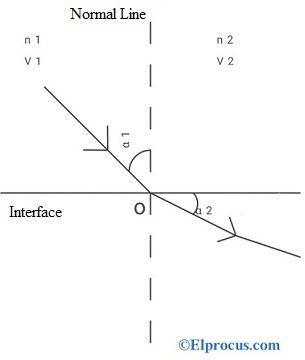

- Emitterkopplad logik används som en logik- och gränssnittsteknik inom extremt höghastighetskommunikationsenheter som fiberoptiska transceivergränssnitt, Ethernet- och ATM-nätverk (Asynchronous Transfer Mode).

- ECL är en logikfamilj baserad på BJT där dess höghastighetsdrift kan uppnås genom att använda en relativt liten spänningssvängning och undvika att transistorerna flyttar in i mättnadsområdet.

- ECL används för att tillverka ASLT-kretsar inom IBM 360/91.

- ECL undviker användningen av staplade transistorer genom att använda en enkelsidig bias i/p och positiv återkoppling mellan primära och sekundära transistorer för att uppnå en inverterfunktion.

- ECL används i extremt höghastighetselektronik.

Detta är alltså en översikt över en emitterkopplad logik eller ECL – krets, funktion, funktioner, egenskaper och applikationer. ECL är den mycket snabbaste logikfamiljen baserad på BJT jämfört med andra digitala logikfamiljer. Den uppnår sin maximala hastighet genom att använda en liten spänningssvängning och undvika att transistorerna rör sig in i mättnadsområdet. Denna logikfamilj ger en otrolig 1ns utbredningsfördröjning och i de senaste ECL-familjerna är denna fördröjning minskad. Här är en fråga till dig, vad är ett alternativt namn för ECL?