JTAG (Joint Test Action Group) är en väletablerad IEEE 1149.1-standard som utvecklades år 1980 för att lösa de tillverkningsproblem som uppstod inom elektroniska kort eller tryckta kretskort . Denna teknik används för att ge tillräckligt med teståtkomst för varje komplext kort när teståtkomsten minskade. Således lanserades gränsavsökningsteknik & JTAG-standarden eller JTAG-specifikation är etablerad. Elektronikens komplexitet har ökat dag för dag, så JTAG-specifikationen har blivit det accepterade testformatet för att testa komplicerade och kompakta elektronikenheter. Den här artikeln diskuterar en översikt av en JTAG protokoll – arbeta med applikationer.

Vad är JTAG?

Namnet som ges till IEEE 1149.1 Standard Test Access Port samt Boundary-Scan Architecture är känt som JTAG (Joint Test Action Group). Denna gränsavsökningsarkitektur används mest inom datorer processorer eftersom den första processorn med JTAG släpptes av Intel. Denna IEEE-standard definierar helt enkelt hur en dators kretsar testas för att bekräfta om den fungerar korrekt efter tillverkningsprocessen. På kretskorten görs tester för att kontrollera lödfogarna.

Joint Test Action Group tillhandahåller en stiftvy för testare med varje IC-platta som hjälper till att identifiera eventuella fel på ett kretskort. När detta protokoll väl har anslutits till ett chip, kan detta fästa en sond till chipet genom att tillåta en utvecklare att styra chipet såväl som dess anslutningar med andra chips. Gränssnittet med gruppen Joint Test Action kan också användas av utvecklare för att kopiera den fasta programvaran till ett icke-flyktigt minne i en elektronisk enhet.

Konfiguration/stift ut

Joint Test Action Group inkluderar 20-stift där varje stift och dess funktion diskuteras nedan.

Pin1 (VTref): Detta är målreferensspänningsstiftet som används för att ansluta till målets huvudströmkälla som sträcker sig från 1,5 till 5,0 VDC.

Pin2 (Vsupply): Detta är målmatningsspänningen som används för att ansluta huvudspänningsförsörjningen för mål 1,5VDC – 5,0VDC.

Pin3 (nTRST): Detta är ett teståterställningsstift som används för att återställa TAP-styrenhetens tillståndsmaskin.

Pins (4, 6, 8, 10, 12, 14, 16, 18 och 20): Dessa är vanliga GND-stift.

Pin5 (TDI): Detta är testdata i stiftet. Denna data flyttas till målenheten. Denna stift måste dras upp i ett definierat tillstånd på målbrädan.

Pin7 (TMS): Detta är testlägesstiftet som dras för att bestämma nästa tillstånd för TAP-styrenhetens tillståndsmaskin.

Pin9 (TCK): Detta är ett testklockstift som synkroniserar den interna tillståndsmaskinens operationer i TAP-styrenheten.

Pin11 (RTCK): Detta är Input Return TCK-stiftet som används i enheter som stöder adaptiv klockning.

Pin13 (TDO): Detta är stiftet Test Data Out, så data flyttas ut från målenheten till flugsmittan.

Pin15 (nSRST): Detta är målsystemets återställningsstift som är anslutet till målets huvudåterställningssignal.

Stift 17 och 19 (NC): Dessa är inte anslutna stift.

JTAG fungerar

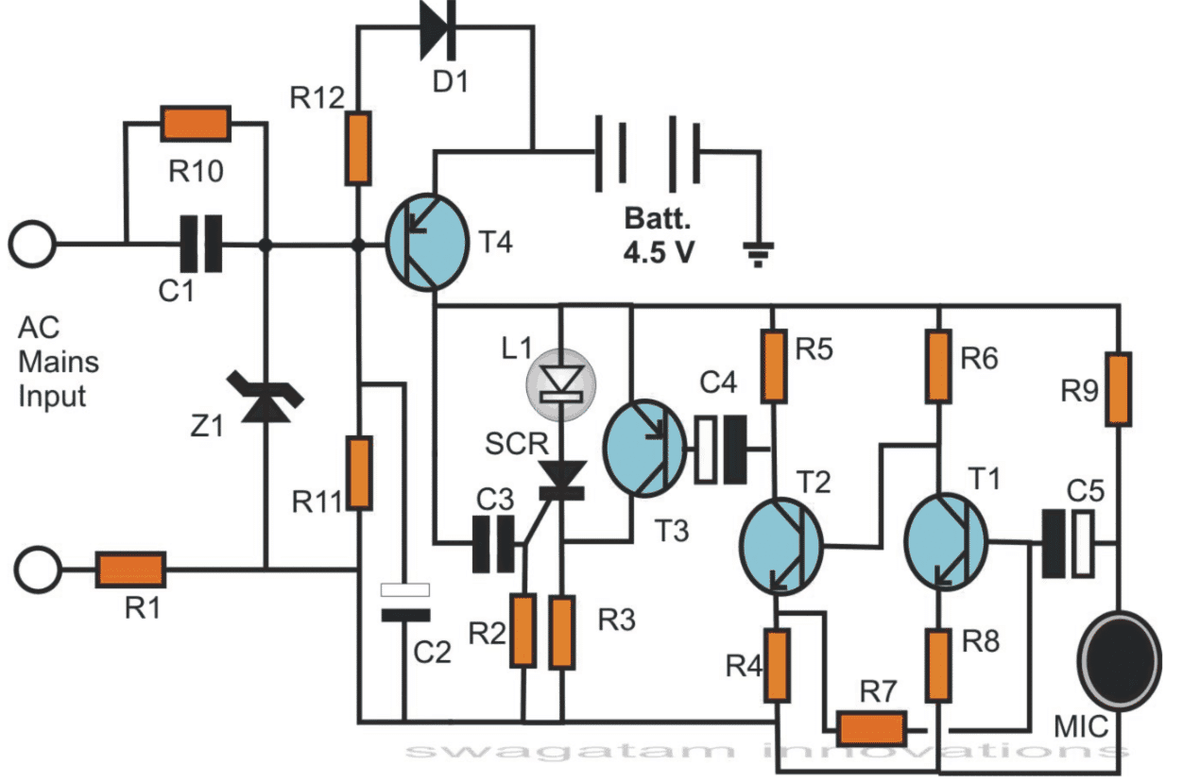

JTAG:s ursprungliga användning är för gränstestning. Här är ett enkelt kretskort inklusive två IC:er som CPU och FPGA . Ett typiskt kort kan innehålla många IC:er. I allmänhet inkluderar IC:er många stift som är anslutna tillsammans med många anslutningar. Här, i följande diagram, visas endast fyra anslutningar.

Så om du designar många brädor där varje bräda har tusentals anslutningar. I det finns det några dåliga brädor. Så vi måste kolla vilken styrelse som fungerar och vilken som inte fungerar. För det utformades Joint Test Action Group.

Detta protokoll kan använda kontrollstiften för alla chips, men i följande diagram kommer Joint Test Action Group att göra alla utgångsstift från CPU och alla ingångsstift på FPGA. Efter det, genom att överföra en viss mängd data från stiften på CPU:n och läsa värdena på stiften från FPGA, säger JTAG att anslutningarna på PCB-kortet är bra.

Egentligen inkluderar Joint Test Action Group fyra logiska signaler TDI, TDO, TMS och TCK. Och dessa signaler måste kopplas ihop på ett speciellt sätt. Till en början är TMS & TCK anslutna parallellt med alla IC:er i JTAG.

Därefter ansluts både TDI och TDO för att bilda en kedja. Som du kan observera inkluderar varje JTAG-kompatibel IC 4-stift som används för JTAG där 3-stift är ingångar och 4:e stift är utmatat. Det femte stiftet som TRST är valfritt. Vanligtvis delas JTAG-stiften inte för andra ändamål.

Genom att använda Joint Test Action Group använder alla IC:er gränstestning som den ursprungliga orsaken skapas av JTAG. För närvarande har användningen av detta protokoll utökats för att tillåta olika saker som att konfigurera FPGA och efter det används JTAG i FPGA-kärnan för felsökningsändamål.

JTAG arkitektur

JTAG-arkitekturen visas nedan. I den här arkitekturen avbryts alla signaler mellan enhetens kärnlogik och stiften genom en seriell skanningsväg som kallas BSR eller Boundary Scan Register. Denna BSR inkluderar olika gränsavsöknings-'celler'. I allmänhet är dessa gränsavsökningsceller inte synliga men de kan användas för att ställa in eller läsa värden i testläge från enhetens stift.

JTAG-gränssnittet som kallas TAP eller Test Access Port använder olika signaler för att stödja gränsavsökningsoperationen som TCK, TMS, TDI, TDO och TRST.

- TCK- eller testklocksignalen synkroniserar helt enkelt insidan av en tillståndsmaskin.

- TMS eller testlägesvalssignal samplas vid den ökande kanten av en testklocksignal för att bestämma nästa tillstånd.

- TDI eller Test Data In-signal betecknar den skiftade datan till testanordningen annars programmeringslogik. När väl den inre tillståndsmaskinen är i rätt tillstånd samplas den vid den ökande kanten av TCK.

- TDO eller Test Data Out-signal betecknar de utskiftade data för testanordningen annars programmeringslogik. När den inre tillståndsmaskinen är i rätt tillstånd är den giltig på den minskande kanten av TCK

- TRST eller Test Reset är ett valfritt stift som används för att återställa TAP-styrenhetens tillståndsmaskin.

TAP-styrenhet

Teståtkomstpunkten i JTAGs arkitektur består av en TAP-kontroller, ett instruktionsregister och testdataregister. Denna styrenhet inkluderar testtillståndsmaskinen som är ansvarig för att läsa TMS- och TCK-signalerna. Här används data i/p-stiftet helt enkelt för att ladda data till gränscellerna mellan IC-kärnan och fysiska stift, och även ladda data till ett av dataregistren eller in i instruktionsregistret. Data-o/p-stiftet används för att läsa data från antingen registren eller gränsceller.

Tillståndsmaskinen för TAP-styrenheten styrs av TMS och den klockas av TCK. State machine använder två vägar för att beteckna två olika lägen som instruktionsläge och dataläge.

Register

Det finns två typer av register tillgängliga inom gränsavsökning. Varje kompatibel enhet inkluderar minst två eller högre dataregister och ett instruktionsregister.

Instruktionsregister

Instruktionsregistret används för att hålla den aktuella instruktionen. Så dess data används av TAP-styrenheten för att bestämma vad som ska utföras med signaler som erhålls. Oftast kommer instruktionsregisterdata att beskriva till vilka av dataregistren signaler som måste skickas.

Dataregister

Dataregistren finns i tre typer: BSR (Boundary Scan Register), BYPASS & ID-KODER-registret. Och även andra dataregister kan finnas där, men de är inte nödvändiga som en del av JTAG-standarden.

Boundary Scan Register (BSR)

BSR är det huvudsakliga testdataregistret som används för att flytta data från och till enhetens I/O-stift.

GÅ FÖRBI

Bypass är ett enbitsregister som används för att skicka data från TDI – TDO. Så det tillåter ytterligare enheter inom en krets att testas med minimal overhead.

ID-KODER

Denna typ av dataregister inkluderar ID-koden samt revisionsnumret för enheten. Så denna data gör att enheten kan anslutas till dess BSDL-fil (Boundary Scan Description Language). Den här filen inkluderade Boundary Scan-konfigurationsdetaljerna för enheten.

Funktionen av JTAG är initialt att instruktionsläget väljs där ett av tillstånden i detta läges 'sökväg' låter operatören klocka inom en instruktion av TDI. Därefter utvecklas statsmaskinen tills den ordnar om. Nästa steg för de flesta instruktioner är att välja dataläge. Så i detta läge laddas data via TDI för att läsas från TDO. För TDI & TDO kommer datavägarna att arrangeras i överensstämmelse med instruktionen som har klockats in. När väl läs/skrivoperationen är klar, utvecklas återigen tillståndsmaskinen till återställningstillståndet.

Skillnaden mellan JTAG och UART

Skillnaden mellan JTAG och UART inkluderar följande.

| JTAG |

UART |

| Termen 'JTAG' står för Joint Test Action Group. | Termen ' UART ” står för Universal Asynchronous Receiver/Transmitter. |

| Det är ett synkront gränssnitt som använder inbyggd hårdvara för programmering av blixten . | UART är ett asynkront gränssnitt som använder en bootloader som körs i minnet. |

| Det är en uppsättning testportar som används för felsökning men som också kan användas för att programmera firmware (vilket ofta görs).

|

UART är en typ av chip som styr kommunikation till och från en enhet, såsom en mikrokontroller, ROM, RAM, etc. För det mesta är det en seriell anslutning som gör att vi kan kommunicera med en enhet. |

| Dessa finns i fyra typer TDI, TDO, TCK, TMS & TRST. | Dessa finns i två typer dumb UART & FIFO UART. |

| Joint Test Action Group är seriell programmering eller dataåtkomstprotokoll som används i gränssnittet för mikrokontroller och relaterade enheter. | En UART är en typ av chip annars mikrokontrollerns underkomponent som används för att tillhandahålla hårdvaran för att generera en asynkron seriell ström som RS-232/RS-485. |

| JTAG-komponenter är processorer, FPGA, CPLD , etc. | UART-komponenter är CLK-generator, I/O-skiftregister, sändnings- eller mottagningsbuffertar, systemdatabussbuffert, läs- eller skrivkontrolllogik, etc. |

JTAG Protocol Analyzer

JTAG Protocol Analyzer som PGY-JTAG-EX-PD är en typ av Protocol Analyzer inklusive några funktioner för att fånga och felsöka kommunikation mellan värd och design som testas. Denna typ av analysator är det ledande instrumentet som gör det möjligt för test- och designingenjörerna att testa de speciella designerna av JTAG för dess specifikationer genom att arrangera PGY-JTAG-EX-PD som Master eller Slave för att generera JTAG-trafik och avkoda avkodningspaketen från Protokoll för Joint Test Action Group.

Funktioner

Funktionerna hos JTAG-protokollanalysatorn inkluderar följande.

- Den stöder upp till 25MH JTAG-frekvenser.

- Den genererar JTAG-trafik och protokollavkodning för bussen samtidigt.

- Den har JTAG Master Capability.

- Variabel JTAG-datahastighet och arbetscykel.

- Användardefinierade TDI & TCK-fördröjningar.

- Värddator USB 2.0 eller 3.0 gränssnitt.

- Felanalys inom Protocol Decode

- Protokollavkodat busstidsdiagram.

- Kontinuerlig strömning av protokolldata till värddatorn för att tillhandahålla en stor buffert.

- Protokollaktivitetslista.

- Vid olika hastigheter kan ett övningsskript skrivas för att kombinera generering av flera dataramar.

Tidsdiagram

De tidsdiagram för JTAG protokollet visas nedan. I följande diagram förblir TDO-stiftet inom högimpedanstillståndet förutom under ett skift-IR/skift-DR-kontrolltillstånd.

I skift-IR- och Shift-DR-kontrollförhållandena uppdateras TDO-stiftet på den minskande kanten av TCK genom Target och samplas på den ökande kanten av TCK genom värd.

Både TDI- och TMS-stiften samplas helt enkelt på den ökande kanten av TCK genom Target. Uppdaterad på avtagande kant annars TCK genom Host.

Ansökningar

De JTAG-applikationer inkluderar följande.

- Joint Test Action Group används ofta i Processorer för att tillhandahålla rätten till inträde till deras emulerings- eller felsökningsfunktioner.

- Alla CPLD och FPGA använder detta som ett gränssnitt för att ge tillgång till sina programmeringsfunktioner.

- Den används för PCB-testning utan fysisk åtkomst

- Den används för tillverkningstester på brädnivå.

Alltså handlar det här om en översikt över JTAG – stiftkonfiguration, arbeta med applikationer. Branschstandarden JTAG används för designverifiering samt PCB-testning efter tillverkning. Här är en fråga till dig, JTAG står för?