Olika typer av digitala system är konstruerade av väldigt få typer av grundläggande nätverkskonfigurationer som AND gate, NAND gate, Eller gate, etc ... Dessa elementära kretsar används om och om igen i olika topologiska kombinationer. Förutom att utföra logik måste digitala system också lagra binära nummer. För dessa minnesceller, även kända som FLIP-FLOP ' s är designade. För att utföra vissa funktioner som binär addition. Därför att utföra sådana funktioner, kombinationer av logiska grindar och FLIP-FLOPs är utformade över en IC med en chip. Dessa IC utgör de praktiska byggstenarna för de digitala systemen. En av sådana byggstenar som används för binär tillägg är Carry Look-ahead Adder.

Vad är en Carry Look-ahead Adder?

En digital dator måste innehålla kretsar som kan utföra aritmetiska operationer såsom addition, subtraktion, multiplikation och division. Bland dessa är addition och subtraktion de grundläggande operationerna medan multiplikation och division är upprepad addition respektive subtraktion.

För att utföra dessa operationer implementeras 'Adder-kretsar' med hjälp av grundläggande logiska grindar. Adder-kretsar utvecklas som Half-adder, Full-adder, Ripple-carry Adder och Carry Look-ahead Adder.

Bland dessa Carry Look-ahead Adder är den snabbare adderkretsen. Det minskar utbredningsfördröjningen, som inträffar under tillsats, genom att använda mer komplexa hårdvarukretsar. Den är designad genom att omvandla krusningsbärande adderkrets så att bärarens logik för adderaren ändras till tvånivålogik.

4-bitars Carry Look-ahead Adder

I parallella adders ges bärutmatningen från varje full adderare som en bäringång till nästa högre ordningstillstånd. Följaktligen är det inte möjligt för dessa adders att producera bär- och summautgångar från något tillstånd om inte en bäringång är tillgänglig för det tillståndet.

Så för att beräkning ska ske måste kretsen vänta tills bärbiten förökas till alla stater. Detta medför fördröjning av bärutbredning i kretsen.

4-bit-Ripple-Carry Adder

Tänk på 4-bitars krusningsbärarkabeln ovan. Här kan summan S3 produceras så snart ingångarna A3 och B3 ges. Men bär C3 kan inte beräknas förrän bärbiten C2 appliceras medan C2 beror på C1. Därför måste bär spridas genom alla stater för att producera slutliga steady-state-resultat. Detta ökar kretsens fördröjningsfördröjning.

Adderarens utbredningsfördröjning beräknas som 'utbredningsfördröjningen för varje grind gånger antalet steg i kretsen'. För beräkning av ett stort antal bitar måste fler steg läggas till, vilket gör förseningen mycket värre. För att lösa denna situation introducerades Carry Look-ahead Adder.

För att förstå funktionen av en Carry Look-ahead Adder beskrivs en 4-bit Carry Look-ahead Adder nedan.

4-bitars-Carry-Look-ahead-Adder-Logic-Diagram

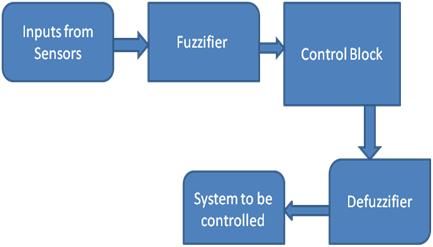

I denna adderare är bäringången i vilket som helst steg i adderaren oberoende av de bärbitar som genereras i de oberoende stegen. Här är utsignalen från vilket steg som helst endast beroende av bitarna som läggs till i föregående steg och den bäringång som tillhandahålls i början. Följaktligen behöver kretsen i vilket som helst steg inte vänta på generering av bärbit från föregående steg och bärbit kan utvärderas när som helst.

Sanningstabellen över bärande blick framåt Adder

För att härleda sanningstabellen för denna adderare introduceras två nya termer - Carry generera och bära propagera. Carry generera Gi = 1 när det finns en bär Ci + 1 genererad. Det beror på Ai- och Bi-ingångar. Gi är 1 när både Ai och Bi är 1. Därför beräknas Gi som Gi = Ai. Bi.

Bärpropagerad Pi är associerad med förökning av bär från Ci till Ci + 1. Det beräknas som Pi = Ai ⊕ Bi. Sanningstabellen för denna adderare kan härledas från att ändra sanningstabellen för en full adderare.

Med hjälp av Gi- och Pi-termerna ges Sum Si och Carry Ci + 1 enligt nedan -

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Därför kan bärbitarna Cl, C2, C3 och C4 beräknas som

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0). P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1) .P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Det kan observeras från ekvationerna som bär Ci + 1 beror bara på bäringen C0, inte på de mellanliggande bärbitarna.

Carry-Look-ahead-Adder-Truth-Table

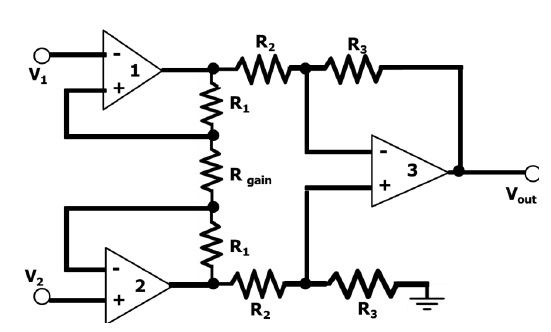

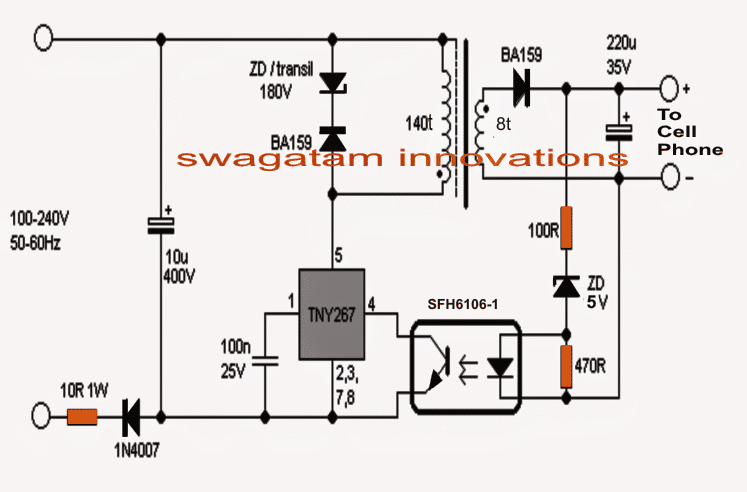

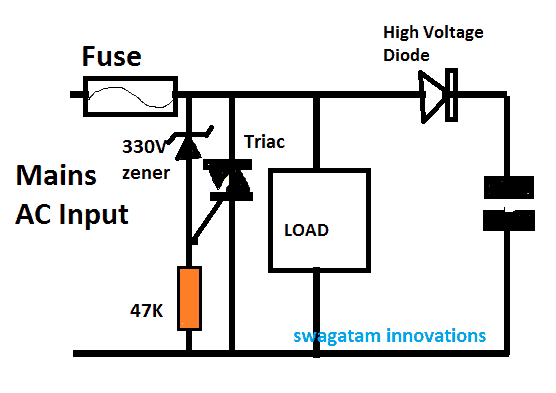

Kretsschema

Ovanstående ekvationer implementeras med användning av två-nivå kombinationskretsar tillsammans med AND-, ELLER-grindar, där grindar antas ha flera ingångar.

Carry-Output-Generation-Circuit-of-Carry-Look-ahead-Adder

Carry Look-ahead Adder-kretsen från 4-bitars ges nedan.

4-bitars-Carry-Look-ahead-Adder-Circuit-Diagram

8-bitars och 16-bitars Carry Look-ahead Adder-kretsar kan utformas genom att kaskadera 4-bitars adderingskrets med bärlogik.

Fördelar med Carry Look-ahead Adder

I denna adderare minskar förökningsfördröjningen. Bärutgången i vilket steg som helst beror bara på den inledande bärbiten i början. Med hjälp av denna adderare är det möjligt att beräkna mellanresultaten. Denna adderare är den snabbaste adderaren som används för beräkning.

Applikationer

High-Speed Carry Look-ahead Adders används som implementerade som IC: er. Därför är det enkelt att bädda in adderaren i kretsar. Genom att kombinera två eller flera adders kan beräkningar av högre booleska funktioner göras enkelt. Här är ökningen av antalet grindar också måttlig när den används för högre bitar.

För denna Adder finns det en avvägning mellan område och hastighet. När den används för högre bitberäkningar ger den hög hastighet men kretsens komplexitet ökar också, vilket ökar det område som kretsen upptar. Denna adderare implementeras vanligtvis som 4-bitarsmoduler som kaskaderas tillsammans när de används för högre beräkningar. Denna adderare är dyrare jämfört med andra tillägg.

För boolesk beräkning på datorer används tillsatser regelbundet. Charles Babbage implementerade en mekanism för att förutse bärbiten i datorer för att minska fördröjningen orsakad av krusningsbärare . Vid utformningen av ett system är beräkningshastigheten den högsta avgörande faktorn för en designer. 1957 patenterade Gerald B. Rosenberger den moderna Binary Carry Look-ahead Adder. Baserat på analysen av grindfördröjning och simulering genomförs experiment för att modifiera kretsen för denna adderare för att göra den ännu snabbare. För en n-bit bär-blick framåt adderare, vad är förökningsfördröjningen, när en fördröjning för varje grind är 20?

Bildkredit