Styrenheten är huvudkomponenten i en central processorenhet (CPU) i datorer som kan styra operationerna under genomförandet av ett program med processorn /dator. Styrenhetens huvudfunktion är att hämta och utföra instruktioner från en dators minne. Den tar emot inmatningsinstruktionen / informationen från användaren och konverterar den till styrsignaler , som sedan ges till processorn för vidare körning. Det ingår som en del av Von Neumann-arkitekturen utvecklad av John Neumann. Det är ansvarigt för att tillhandahålla tidssignaler, och styr signaler och styr körningen av ett program av CPU: n. Den ingår som en intern del av processorn i moderna datorer. Den här artikeln beskriver fullständig information om styrenheten.

Vad är kontrollenheten?

Komponenten som tar emot insignalen / informationen / instruktionen från användaren och omvandlas till styrsignaler för körning i CPU: n. Den styr och styr huvudminnet, aritmetik- och logikenheten (ALU), in- och utmatningsenheter, och ansvarar också för instruktionerna som skickas till datorns CPU. Den hämtar instruktionerna från huvudminne av en processor och skickas till processorinstruktionsregistret, som innehåller registerinnehåll.

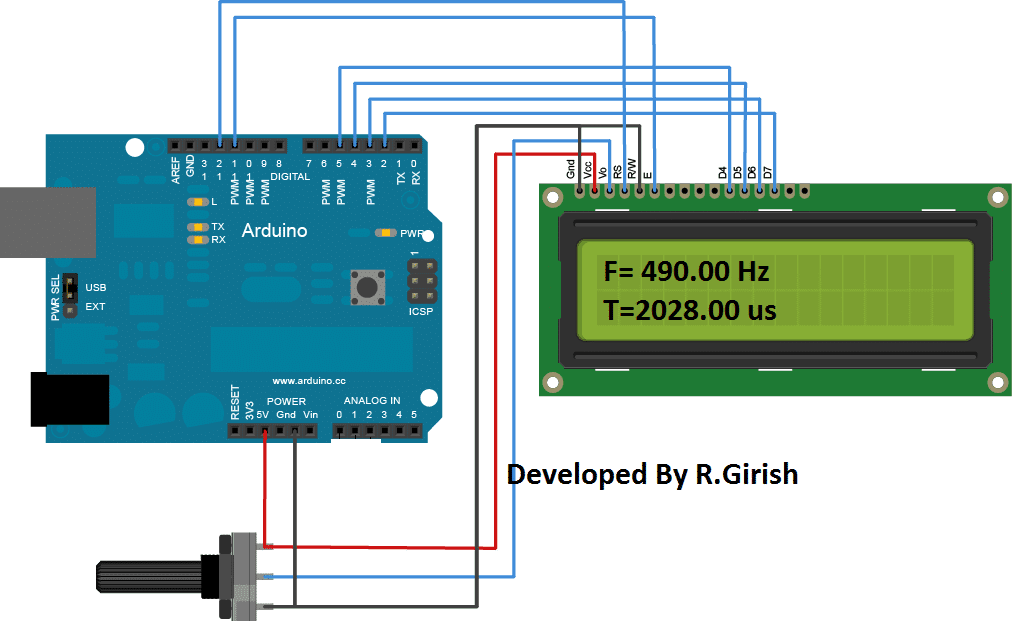

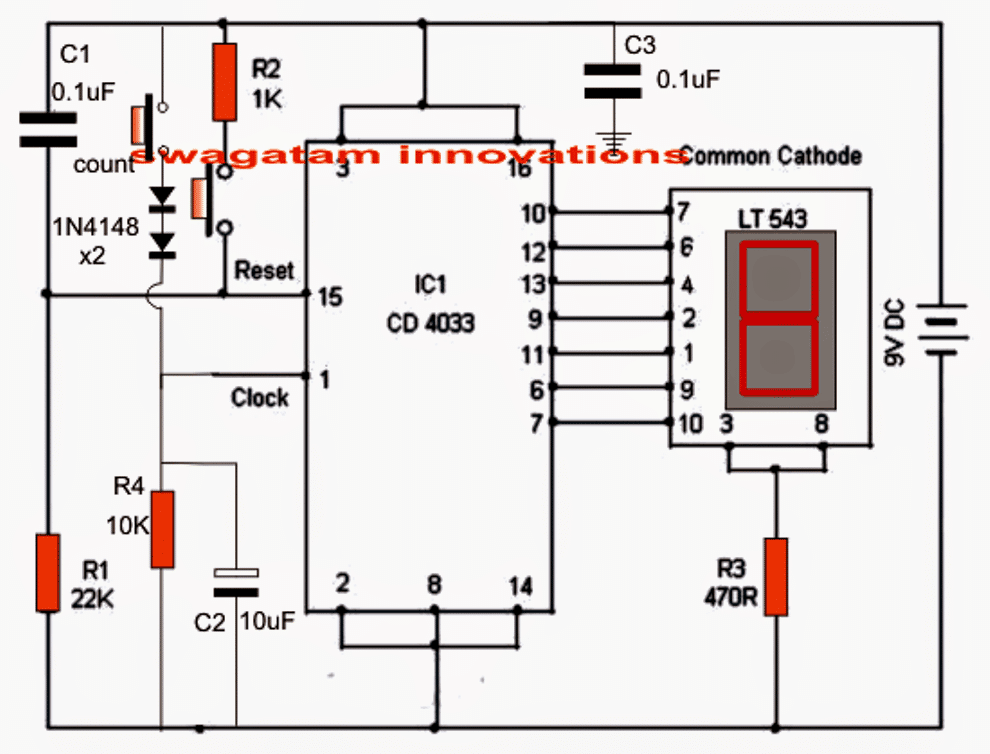

Kontrollschema blockdiagram

Styrenheten omvandlar ingången till styrsignaler och skickas sedan till processorn och styr genomförandet av ett program. Åtgärderna som måste utföras styrs av processorn på datorn. Huvudsakligen Central Processing Unit (CPU) och Enhet för grafisk bearbetning (GPU) kräver en styrenhet som den interna delen. Blockdiagrammet för styrenheten visas ovan.

Komponenter i en styrenhet

Komponenterna i denna enhet är instruktioner register , styrsignaler i CPU: n, styrsignaler till / från bussen, styrbuss, ingångsflaggor och klocksignaler.

Komponenterna i den trådbundna styrenheten är instruktionsregister (innehåller opkod och adressfält), tidsenhet, styrtillstånd generator , styrsignalgenereringsmatris och instruktionsavkodare.

Komponenterna i den mikroprogrammerade styrenheten är nästa adressgenerator, ett styradressregister, styrminne och styrdataregister.

Funktioner

De styrenhetens funktioner inkluderar följande.

- Den styr flödet av datasekvens mellan processorn och andra enheter.

- Det kan tolka instruktionerna och kontrollera dataflödet i processorn.

- Den genererar sekvensen av styrsignaler från de mottagna instruktionerna eller kommandon från instruktionsregistret.

- Det har ansvaret för att styra exekveringsenheter som ALU, databuffertar och register i CPU: n på en dator.

- Det har förmågan att hämta, avkoda, hantera körningen och lagra resultat.

- Det kan inte bearbeta och lagra data

- För att överföra data kommunicerar den med in- och utdataenheterna och styr alla enheter på datorn.

Design av styrenhet

Utformningen av detta kan göras med två typer av styrenhet som inkluderar följande.

- Hardwire-baserad

- Mikroprogrammerad baserad (ennivå och två nivåer)

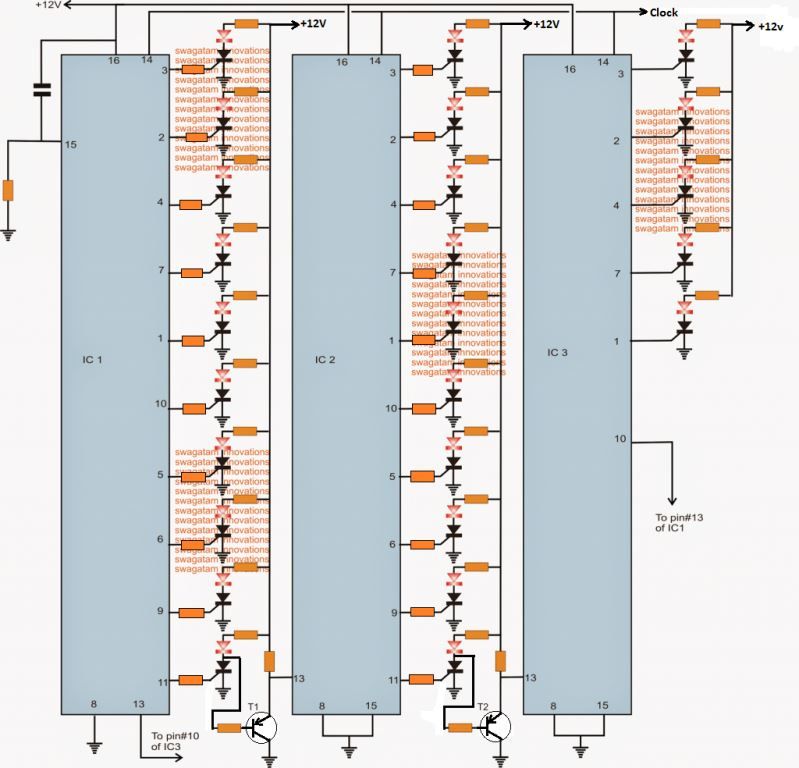

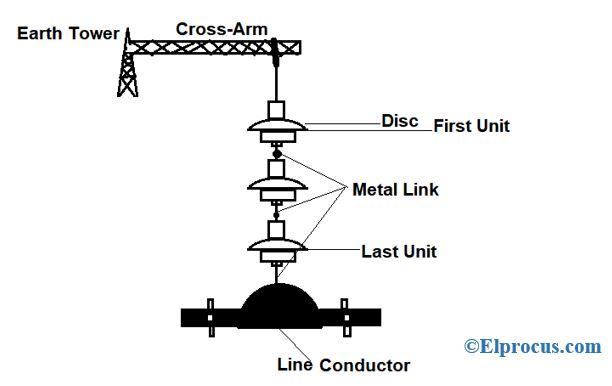

Kabelansluten styrenhet

Den grundläggande utformningen av en trådbunden styrenhet visas ovan. I denna typ genereras styrsignalerna av en speciell hårdvara logikkrets utan någon förändring i kretsstrukturen. I detta kan den genererade signalen inte modifieras för körning i processorn.

Grunddata för en opcode (operationskod för en instruktion skickas till instruktionsavkodaren för avkodning. Instruktionen avkodare är en uppsättning avkodare för att avkoda olika typer av data i opkoden. Detta resulterar i utsignaler som innehåller värden på aktiva signaler som ges som ingång till matrisgeneratorn för att generera styrsignaler för exekvering av ett program av datorns processor.

Hardwire-baserad styrenhet

Matrisgeneratorn tillhandahåller tillstånd för styrenheten och signalerna från processorn (avbrottssignaler). Matrix är byggd som programmerbar logisk matris . Styrsignalerna som genereras av matrisgeneratorn ges som ingång till nästa generatormatris och kombineras med tidssignalerna för tidsenheten som innehåller rektangulära mönster.

För att hämta ny instruktion förvandlas styrenheten till ett första steg för utförande av ny instruktion. Styrenheten förblir i det initiala steget eller det första steget så länge tidssignalerna, ingångssignalerna och instruktionstillstånden för en dator är oförändrade. Ändringen av styrenhetens tillstånd kan höjas om någon förändring av någon av de genererade signalerna uppstår.

När en extern signal eller avbrott inträffar går styrenheten till nästa tillstånd och utför behandlingen av avbrottssignalen. Flaggorna och tillstånden används för att välja önskade tillstånd för att utföra instruktionscykeln.

I det sista tillståndet hämtar styrenheten nästa instruktion och skickar utmatningen till programräknaren, sedan till minnesadressregistret, till buffertregistret och sedan till instruktionsregistret för att läsa instruktionen. Slutligen, om den sista instruktionen (som hämtas av styrenheten) är slutinstruktion, går den till processorns driftstillstånd och väntar tills användaren riktar nästa program.

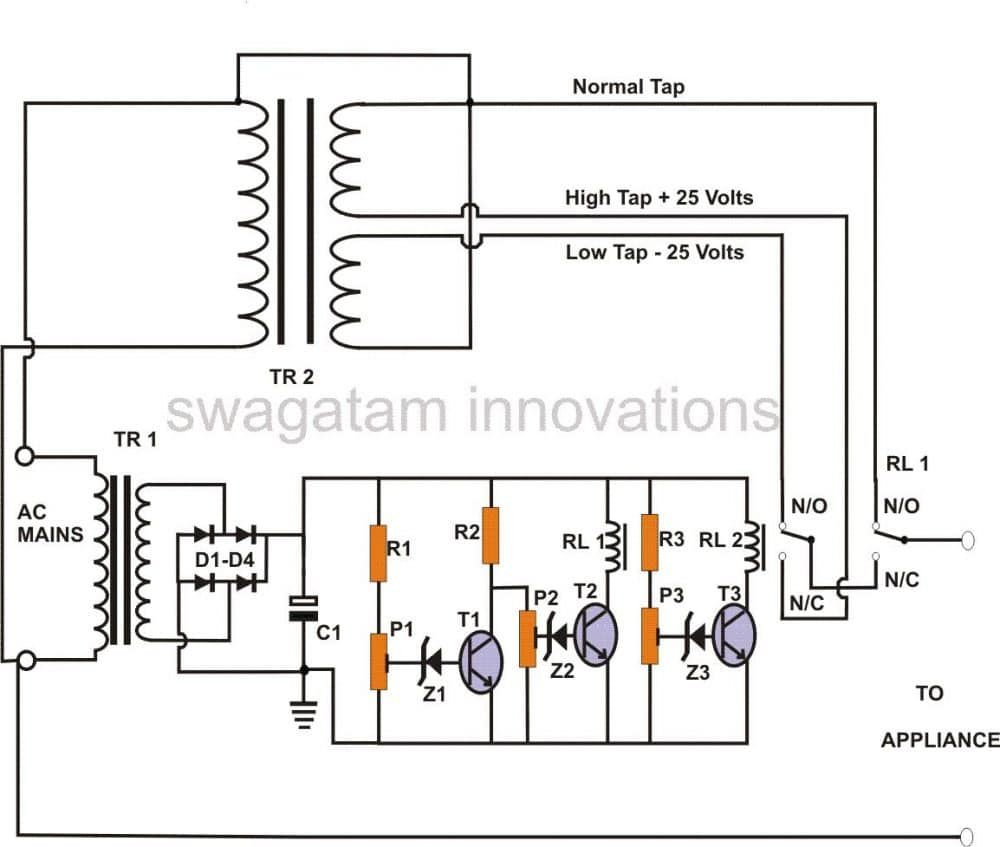

Mikroprogrammerad styrenhet

I denna typ används styrlagret för att lagra styrsignalerna som kodas under genomförandet av ett program. Styrsignalen genereras inte omedelbart och avkodas eftersom mikroprogrammet lagrar adressfältet i styrlagret. Hela processen är en enda nivå.

Mikrooperationerna görs för genomförande av mikroinstruktioner i programmet. Blockdiagrammet för den mikroprogrammerade styrenheten visas ovan. Från diagrammet erhålls adressen till mikroinstruktionen från styrminnets adressregister. All information från styrenheten lagras permanent i kontrollminnet som kallas ROM.

Mikroprogrammerad styrenhet

Mikroinstruktionen från styrminnet hålls av kontrollregistret. Eftersom mikroinstruktionen är i form av kontrollord (innehåller binära styrvärden) som behöver 1 eller flera mikrooperationer för att kunna bearbetas.

Under utförandet av mikroinstruktioner beräknade nästa adressgenerator nästa adress för mikroinstruktionen och skickade sedan till styradressregistret för att läsa nästa mikroinstruktion.

Sekvensen av mikrooperationer i ett mikroprogram utförs av nästa adressgenerator och fungerar som mikroprogramsekvenserare för att få sekvensadressen, dvs.

Verilog-kod för styrenheten

Verilog-kod för styrenhet visas nedan.

`inkludera“ prj_definition.v ”

modul CONTROL_UNIT (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_

// Utgångssignaler

// Utgångar för registerfil

utgång [`DATA_INDEX_LIMIT: 0] RF_DATA_W

utgång [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

utgång RF_READ, RF_WRITE

// Utgångar för ALU

utdata [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

utgång [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Utgångar för minne

utdata [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

utgång MEM_READ, MEM_WRITE

// Ingångssignaler

ingång [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

ingång ZERO, CLK, RST

// Utgående signal

inout [`DATA_INDEX_LIMIT: 0] MEM_DATA

// Statliga nät

tråd [2: 0] proc_state

// håller programräknarvärde, lagrar den aktuella instruktionen, staplar pekarregistret

reg MEM_READ, MEM_WRITE

reg MEM_ADDR

reg ALU_OP1, ALU_OP2

reg ALU_OPRN

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reg RF_DATA_W

reg [1: 0] state, next_state

PROC_SM state_machine (.STATE (proc_state) ,. CLK (CLK), RST (RST))

alltid @ (posedge CLK)

Börja

om (RST)

stat<= RST

annan

stat<= next_state

slutet

alltid @ (stat)

Börja

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1’b0 ALU_OP2 = 1’b0 ALU_OPRN = 1’b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

fall (tillstånd)

`PROC_FETCH: börja

nästa_stat = `PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1’b1

slutet

`PROC_DECODE: börja

nästa_stat = `PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

slutet

`PROC_EXE: börja

nästa_stat = `PROC_MEM

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

RF_ADDR_R1 = 1’b0

slutet

`PROC_MEM: börja

nästa_stat = `PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

slutet

`PROC_WB: börja

nästa_stat = `PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

slutet

endcase

slutet

slutmodul

modul PROC_SM (STATE, CLK, RST)

// lista över ingångar

ingång CLK, RST

// lista över utgångar

utgång [2: 0] STATE

// ingångslista

ingång CLK, RST

// utgångslista

utgång STAT

reg [2: 0] STAT

reg [1: 0] tillstånd

reg [1: 0] nästa_stat

reg PC_REG, INST_REG, SP_REF

`definiera PROC_FETCH 3’h0

`definiera PROC_DECODE 3’h1

`definiera PROC_EXE 3’h2

`definiera PROC_MEM 3’h3

`definiera PROC_WB 3’h4

// initiering av tillstånd

första

Börja

tillstånd = 2’bxx

nästa_stat = `PROC_FETCH

slutet

// återställ signalhantering

alltid @ (posedge RST)

Börja

state = `PROC_FETCH

nästa_stat = `PROC_FETCH

slutet

alltid @ (posedge CLK)

Börja

tillstånd = nästa_stat

slutet

alltid @ (stat)

Börja

om (ange === `PROC_FETCH)

Börja

nästa_stat = `PROC_DECODE

utskriftsinstruktion (INST_REG)

slutet

om (ange === `PROC_DECODE)

Börja

nästa_stat = `PROC_EXE

slutet

om (ange === `PROC_EXE)

Börja

nästa_stat = `PROC_MEM

utskriftsinstruktion (SP_REF)

slutet

om (ange === `PROC_MEM)

Börja

nästa_stat = `PROC_WB

slutet

om (ange === `PROC_WB)

Börja

nästa_stat = `PROC_FETCH

utskriftsinstruktion (PC_REG)

slutet

slutet

uppgift utskriftsinstruktion

ingång [`DATA_INDEX_LIMIT: 0] inst

reg [5: 0] opkod

reg [4: 0] rs

reg [4: 0] rt

reg [4: 0] rd

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] omedelbar reg [25: 0] adress

Börja

// analysera instruktionen

// R-typ

{opcode, rs, rt, rd, shamt, funct} = inst

// Jag skriver

{opcode, rs, rt, omedelbar} = inst

// J-typ

{opcode, adress} = inst

$ skriv (“@% 6dns -> [0X% 08h]“, $ tid, inst)

case (opcode) // R-Type

6'h00: start

fall (funktion)

6’h20: $ skriv (“lägg till r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h22: $ skriv (“sub r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6'h2c: $ skriv ('mul r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h24: $ skriv (“och r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6'h25: $ skriv ('eller r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'h27: $ skriv ('nor r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'h2a: $ skriv ('slt r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h00: $ skriv (“sll r [% 02d],% 2d, r [% 02d]”, rs, shamt, rd)

6’h02: $ skriv (“srl r [% 02d], 0X% 02h, r [% 02d]”, rs, shamt, rd)

6’h08: $ skriv (“jr r [% 02d]”, rs)

standard: $ skriv (“”)

endcase

slutet

// Jag skriver

6'h08: $ skriv ('addi r [% 02d], r [% 02d], 0X% 04h', rs, rt, omedelbar)

6’h1d: $ skriv (“muli r [% 02d], r [% 02d], 0X% 04h”, rs, rt, omedelbar)

6'h0c: $ skriv ('andi r [% 02d], r [% 02d], 0X% 04h', rs, rt, omedelbar)

6'h0d: $ skriv ('ori r [% 02d], r [% 02d], 0X% 04h', rs, rt, omedelbar)

6’h0f: $ skriv (“lui r [% 02d], 0X% 04h”, rt, omedelbar)

6'h0a: $ skriv ('slti r [% 02d], r [% 02d], 0X% 04h', rs, rt, omedelbar)

6'h04: $ skriv ('beq r [% 02d], r [% 02d], 0X% 04h', rs, rt, omedelbar)

6’h05: $ skriv (“bne r [% 02d], r [% 02d], 0X% 04h”, rs, rt, omedelbar)

6’h23: $ skriv (“lw r [% 02d], r [% 02d], 0X% 04h”, rs, rt, omedelbar)

6'h2b: $ skriv ('sw r [% 02d], r [% 02d], 0X% 04h', rs, rt, omedelbar)

// J-typ

6'h02: $ skriv ('jmp 0X% 07h', adress)

6’h03: $ skriv (“jal 0X% 07h”, adress)

6'h1b: $ skriv ('push')

6'h1c: $ skriv ('pop')

standard: $ skriv (“”)

endcase

$ skriv (“ n”)

slutet

slutuppgift

slutmodul

Vanliga frågor

1). Vad fungerar en styrenhet?

Styrenhetens arbete är att styra flödet av data eller instruktioner för körning av processorn av en dator. Den styr, hanterar och koordinerar huvudminnet, ALU, register, ingångar och utdataenheter. Den hämtar instruktionerna och genererar styrsignaler för körningen.

2). Vad är kontrollminnet?

Kontrollminne är vanligtvis RAM eller ROM för att lagra adress och data för kontrollregistret.

3). Vad är Wilkes kontrollenhet?

Den sekventiella och kombinationskretsar av den trådbundna styrenheten ersätts av Wilkes-styrenheten. Den använder en lagringsenhet för att lagra sekvensen för instruktioner för ett mikroprogram.

4). Vad är en fastkopplad styrenhet?

Den trådbundna styrenheten genererar styrsignalerna genom att byta från ett tillstånd till ett annat tillstånd i varje klockpuls utan någon fysisk förändring i kretsen. Generering av styrsignaler beror på instruktionsregister, avkodare och avbrottssignaler.

5). Vad är kontrollminnet?

Informationen från styrenheten eller data lagras tillfälligt eller permanent i styrminnet.

Kontrollminnet är av två typer. De är Random Access Memory (RAM) och Read-Only Memory (ROM).

Således handlar det här om definitionen, komponenter, design, diagram, funktioner och typer av styrenhet . Här är en fråga till dig, 'Vad är syftet med kontrolladressregistret?'