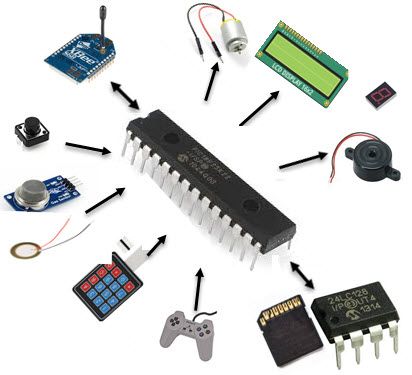

Instruktionsuppsättning eller instruktionsuppsättningsarkitektur är strukturen på datorn som ger kommandon till datorn för att vägleda datorn för bearbetning av datamanipulation. Instruktionsuppsättningen består av instruktioner, adresseringslägen, inbyggda datatyper, register, avbrott, undantagshantering och minnesarkitektur. Instruktionsuppsättningen kan emuleras i programvara med hjälp av en tolk eller inbyggd i maskinvaran för processorn. Instruktionsuppsättningsarkitektur kan betraktas som en gräns mellan programvaran och hårdvaran. Klassificering av mikrokontroller och mikroprocessorer kan göras baserat på RISC och CISC instruktionsuppsättningsarkitektur.

Instruktionsuppsättning av processor

Instruktionsuppsättning specificerar processorns funktionalitet inklusive de processer som stöds av processorn, lagringsmekanismer för processorn och sättet att kompilera programmen till processorn.

Vad är RISC och CISC?

De RISC och CISC kan utökas enligt följande:

RISC representerar Reduced Instruction Set Computer och

CISC representerar Complex Instruction Set Computer.

RISC (Reduced Instruction Set Computer) Arkitektur

RISC-arkitektur

De mikrokontrollarkitektur som använder små och mycket optimerade instruktioner kallas Reduced Instruction Set Computer eller helt enkelt kallad RISC. Det kallas också som LOAD / STORE-arkitektur.

I slutet av 1970-talet och början av 1980-talet utvecklades RISC-projekt främst från Stanford, UC-Berkley och IBM. John Coke från IBMs forskargrupp utvecklade RISC genom att minska antalet instruktioner som krävs för att bearbeta beräkningar snabbare än CISC. RISC-arkitekturen är snabbare och de marker som krävs för tillverkning av RISC-arkitektur är också billigare jämfört med CISC-arkitekturen.

Typiska funktioner i RISC-arkitektur

- Rörledningsteknik för RISC, kör flera delar eller steg av instruktioner samtidigt så att varje instruktion på CPU: n optimeras. Därför har RISC-processorerna Clock per instruktion för en cykel, och detta kallas som One Cycle Execution.

- Det optimerar användning av register med mer antal register i RISC och mer antal interaktioner i minnet kan förhindras.

- Enkla adresseringslägen, till och med komplex adressering kan göras med hjälp av aritmetik OCH / ELLER logiska operationer .

- Det förenklar kompileringsdesignen genom att använda identiska register för allmänna ändamål som gör att alla register kan användas i vilket sammanhang som helst.

- För effektiv användning av registren och optimering av rörledningsanvändningarna krävs en reducerad instruktionsuppsättning.

- Antalet bitar som används för opkoden reduceras.

- I allmänhet finns det 32 eller fler register i RISC.

Fördelar med RISC-processorarkitektur

- På grund av den lilla uppsättningen instruktioner från RISC kan högkvalitativa språkkompilatorer producera mer effektiv kod.

- RISC tillåter friheten att använda utrymmet på mikroprocessorer på grund av dess enkelhet.

- I stället för att använda Stack använder många RISC-processorer registren för att skicka argument och hålla de lokala variablerna.

- RISC-funktioner använder bara några få parametrar, och RISC-processorerna kan inte använda samtalsinstruktionerna och använder därför instruktioner med fast längd som är lätta att pipeline.

- Operationshastigheten kan maximeras och körtiden kan minimeras.

- Mycket mindre antal instruktionsformat (mindre än fyra), ett fåtal instruktioner (cirka 150) och några adresseringslägen (mindre än fyra) behövs.

Nackdelar med RISC-processorarkitektur

- Med den ökade längden på instruktionerna ökar komplexiteten för RISC-processorer att utföra på grund av dess karaktärscykel per instruktion.

- RISC-processornas prestanda beror främst på kompilatorn eller programmeraren, eftersom kompilatorns kunskap spelar en viktig roll när man konverterar CISC-koden till en RISC-kod, därför beror kvaliteten på den genererade koden på kompilatorn.

- Under omplaneringen av CISC-koden till en RISC-kod, benämnd som en kodutvidgning, ökar storleken. Och kvaliteten på denna kodutvidgning beror igen på kompilatorn och även på maskinens instruktionsuppsättning.

- Den första nivån cache för RISC-processorer är också en nackdel med RISC, där dessa processorer har stora minnescacher på själva chipet. För att mata instruktionerna kräver de mycket snabba minnessystem .

CISC (Complex Instruction Set Computer) Arkitektur

Huvudsyftet med CISC-processorarkitekturen är att slutföra uppgiften genom att använda färre antal monteringslinjer. För detta ändamål är processorn byggd för att utföra en serie operationer. Komplex instruktion kallas också MULT, som fungerar minnesbanker på en dator direkt utan att kompilatorn utför lagrings- och laddningsfunktioner.

CISC-arkitektur

Funktioner i CISC Architecture

- För att förenkla datorarkitekturen stöder CISC mikroprogrammering.

- CISC har fler fördefinierade instruktioner som gör det enkelt att utforma och implementera språk på hög nivå.

- CISC består av mindre antal register och mer antal adresseringslägen, i allmänhet 5 till 20.

- CISC-processor tar varierande cykeltid för att utföra instruktioner - flerklockcykler.

- På grund av CISC: s komplexa instruktionsuppsättning är rörledningstekniken mycket svår.

- CISC består av fler instruktioner, i allmänhet från 100 till 250.

- Särskilda instruktioner används mycket sällan.

- Operationer i minnet manipuleras av instruktioner.

Fördelar med CISC-arkitektur

- Varje maskinspråkinstruktion grupperas i en mikrokodinstruktion och utförs i enlighet därmed och lagras sedan inbyggt i huvudprocessorns minne, benämnt som mikrokodimplementering.

- Eftersom mikrokodminnet är snabbare än huvudminnet kan mikrokodsinstruktionsuppsättningen implementeras utan avsevärd hastighetsminskning jämfört med hårdkopplad implementering.

- Hela nya instruktionsuppsättningar kan hanteras genom att modifiera mikroprogrammets design.

- CISC, antalet instruktioner som krävs för att genomföra ett program kan minskas genom att bygga rikt instruktionsuppsättningar och kan också göras att använda långsamt huvudminne mer effektivt.

- På grund av övermängden av instruktioner som består av alla tidigare instruktioner gör det mikrokodning enkelt.

Nackdelar med CISC

- Mängden klocktid som olika instruktioner tar kommer att vara annorlunda - på grund av detta sänks maskinens prestanda.

- Instruktionsuppsättningens komplexitet och chipmaskinvaran ökar eftersom varje ny version av processorn består av en delmängd av tidigare generationer.

- Endast 20% av de befintliga instruktionerna används i en typisk programmeringshändelse, även om det finns många specialinstruktioner som inte ens används ofta.

- Villkorliga koder ställs in av CISC-instruktionerna som en bieffekt av varje instruktion som tar tid för denna inställning - och när den efterföljande instruktionen ändrar tillståndskodbitarna - så måste kompilatorn undersöka tillståndskodbitarna innan detta händer.

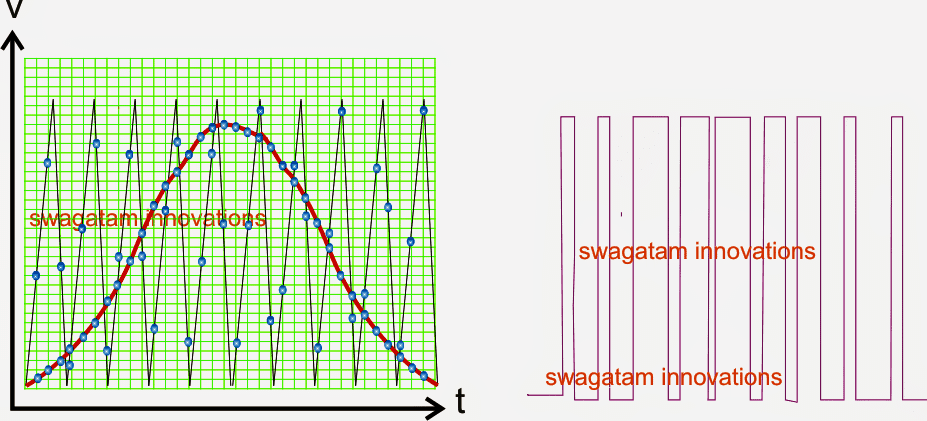

RISC Vs. CISC

- Slöserierna kan förhindras av programmeraren genom att ta bort onödig kod i RISC, men medan du använder CISC-koden leder det till slöserier på grund av ineffektiviteten hos CISC.

- I RISC är varje instruktion avsedd att utföra en liten uppgift så att, för att utföra en komplex uppgift, används flera små instruktioner tillsammans, medan endast få instruktioner krävs för att göra samma uppgift med CISC - eftersom den kan utföra komplex uppgift eftersom instruktionerna liknar en högspråkig kod.

- CISC används vanligtvis för datorer medan RISC används för smarta telefoner, surfplattor och andra elektroniska enheter.

Följande bild visar fler skillnader mellan RISC och CISC

RISC Vs. CISC

Således diskuteras den här artikeln om RISC och CISC arkitekturen funktioner i RISC och CISC processorer arkitektur fördelar och nackdelar med RISC och CISC, och skillnader mellan RISC och CISC arkitekturer med en kort idé. För mer information om RISC- och CISC-arkitekturen, vänligen skicka dina frågor genom att kommentera nedan.

Fotokrediter:

- Instruktionsuppsättning av Processor av arstechnica

- RISC Architecture av LSI-tävling

- RISC vs. CISC av csarassignment