ARM (Advanced RISC Machine) har lanserat flera processorer som har olika funktioner såväl som olika kärnor för en mängd olika applikationer. Den första ARM-arkitekturen har 26-bitarsprocessorer, men nu nådde den 64-bitarsprocessorer. Den allmänna expansionen av ARM-produkter kan inte kategoriseras i viss viss information. Men ARM-produkter kan förstås utifrån dess arkitektur. Standardprocessorerna i ARM-serien som finns på marknaden börjar från ARM7 till ARM11. Dessa processorer har flera funktioner som cache, Data Tightly Coupled-minne, MPU, MMU, etc. Några av de allmänt kända ARM-processorserierna är ARM926EJ-S, ARM7TDMI och ARM11 MPCore. Denna artikel är särskilt avsedd för ARM7-baserad LPC2148 mikrokontroller arkitekturöversikt som ger dig kort information om mikrokontrollern arkitektur.

ARM7-baserad LPC2148 mikrokontrollerarkitektur

ARM7 är ett 32-bitars allmänt ändamål mikroprocessor , och det erbjuder några av funktionerna som lite strömförbrukning och hög prestanda. Arkitekturen för en ARM är beroende av principerna för RISC . Den tillhörande avkodningsmekanismen, liksom RISC-instruktionsuppsättningen, är mycket lätt när vi jämför med mikroprogrammerad CISC -Komplexa instruktionsdatorer.

Pipeline-metoden används för att bearbeta alla block i arkitekturen. I allmänhet utförs en enda instruktionsuppsättning, därefter översätts dess ättling, & a 3rd-instruktion erhålls från minnet.

En exklusiv arkitektonisk plan för ARM7 kallas Thumb, och den passar perfekt för applikationer med hög volym där kompakt kod är en fråga. ARM7 använder också en exklusiv arkitektur, nämligen Thumb. Det gör det perfekt för olika applikationer med minnesbegränsningar där tätheten av kod är en fråga.

ARM7-baserad mikrokontroller (LPC2148) Arkitektur

Avbryt källor

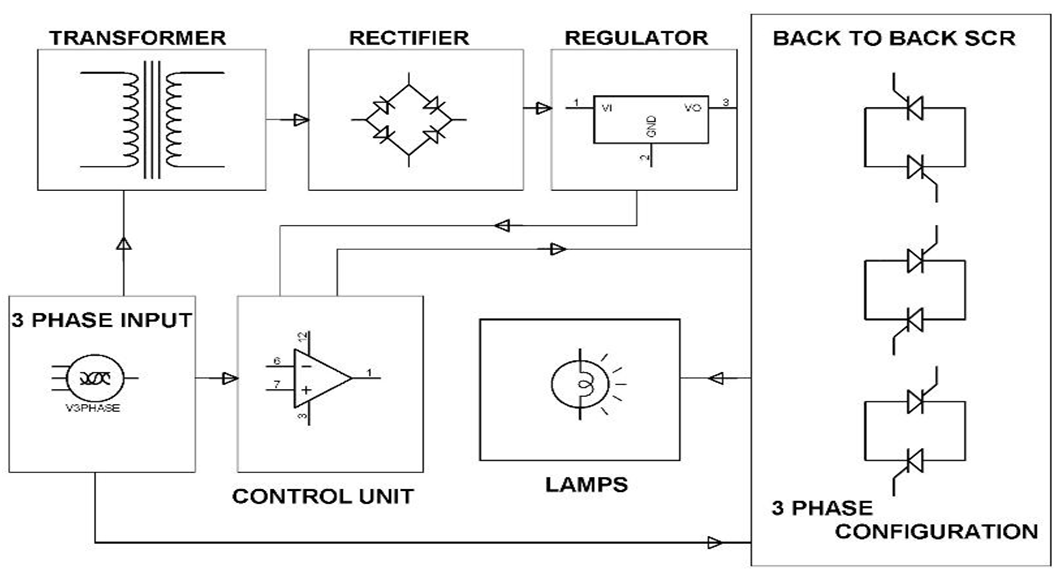

Varje kringutrustning består av en enda avbrottslinje knuten till VIC (vektoravbrottsstyrenhet), även om den kan ha olika avbrottsflaggor inuti. Enskilda avbrottsflaggor kan också beteckna en eller flera avbrottsresurser.

Flash-programminne på chip

Mikrokontrollern LPC2141 / 42/44/46/48 inkluderar ett flashminne som 32 kilobyte, kilobyte, 128 kilobyte respektive 256 kilobyte. Detta flashminne kan användas för både datalagring och kod. Programmeringen av flashminnet kan göras i systemet via den seriella porten.

Programapplikationen kan också raderas medan applikationen körs, vilket möjliggör flexibilitet för datalagringsförbättringar av firmware osv. På grund av valet av en arkitektonisk lösning för en startladdare på chip, är det tillgängliga minnet för mikrokontrollerna LPC2141 / 42 / 44/46/48 är 32 kilobyte, kilobyte, 128 kilobyte, 256 kilobyte och 500 kilobyte. Flashminnet för dessa mikrokontroller erbjuder 1 00 000 radering per cykel och datakonservering under många år.

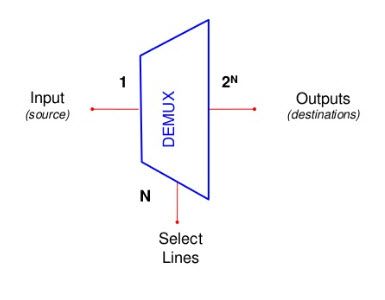

Pin Connect Block

Detta block tillåter valda stift på ARM7-baserade LPC2148 mikrokontroller för att ha flera funktioner. Multiplexrarna kan styras av konfigurationsregisterna för att tillåta länken mellan stiftet och kringutrustning på chipet.

Kringutrustning måste kopplas till lämpliga stift innan de utlöses och innan anslutna avbrott tillåts. Mikrokontrollerfunktionaliteten kan definieras av stiftkontrollmodulen genom dess stiftval av register i en viss hårdvarumiljö.

Efter att ha ordnat om alla portar av portar (port 0 och port 1) är ordnade som i / p enligt de givna undantagen. Om felsökning är tillåten

Om felsökning är tillåtet kommer JTAG-stiften att gissa funktionerna hos JTAG. Om ett spår är tillåtet, kommer spårningsstiftet att gissa funktionens funktion. Stiften anslutna till I2C0- och I2C1-stiften är öppna.

GPIO- Allmänt Parallell in- / utgång

GPIO-register styr enhetsstift som inte är länkade till en viss perifer funktion. Enhetsstiften kan ordnas som i / p [s eller o / ps. Enskilda register gör det möjligt att rensa valfritt antal o / p samtidigt. Utgångsregistrets värde kan avläsas och portens stiftens nuvarande tillstånd. Dessa mikrokontroller startar en accelererad funktion över LPC200-enheter.

Allmänna ingångs- / utgångsregister flyttas till processorbussen som används för bästa möjliga I / O-tid.

- Dessa register är adresserbara byte.

- Det totala värdet på en port kan vara

- Portens fullständiga värde kan skrivas i den enda instruktionen

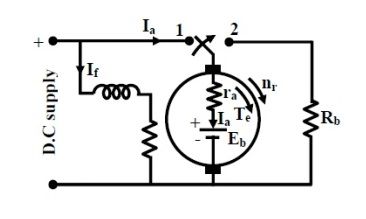

10-bitars ADC (analog till digital omvandlare)

Mikrokontrollerna som LPC2141 eller 42 innehåller två ADC-omvandlare , och dessa är bara 10-bitars har en och LPC2144 / 46/48 har två ADC: er, och dessa är bara 10-bitars raka approximation ADC: er. Även om ADC0 innehåller 6-kanaler och ADC1 har 8-kanaler. Således är antalet tillgängliga ADC i / ps för LPC2141 eller 42 6 & 14 för LPC2141 eller 42.

10-bitars DAC (digital till analog omvandlare)

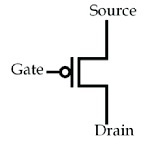

DAC tillåter dessa mikrokontroller att producera en utbytbar analog o / p och VREFär den största utdata av a digital till en analog Spänning.

Device Controller-USB 2.0

Den universella seriella bussen består av 4-ledare, och det ger stöd för kommunikation mellan ett antal kringutrustning och värdar. Denna styrenhet tillåter USB-bredd för anslutning av enheter med hjälp av ett protokoll baserat på token.

Bussen stöder frånkoppling av hot plugging och dynamisk insamling av enheterna. Varje kommunikation startas via värdkontrollern. Dessa mikrokontroller är utformade med en universell seriell bussapparatstyrenhet som tillåter 12 Mbit / sek-data som ersätts av en USB-värdstyrenhet.

UARTs

Dessa mikrokontroller inkluderar två UART för standardöverföring och få datalinjer. I motsats till tidigare mikrokontroller (LPC2000) initierar UART i mikrokontroller LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 en partiell baudfrekvensgenerator som används för båda UART-enheterna, vilket gör att dessa typer av mikrokontroller kan uppnå typiska baudhastigheter som 115200 för varje kristallfrekvens över 2 MHz . Dessutom utförs kontrollfunktionerna som CTS / RTS helt i hårdvara.

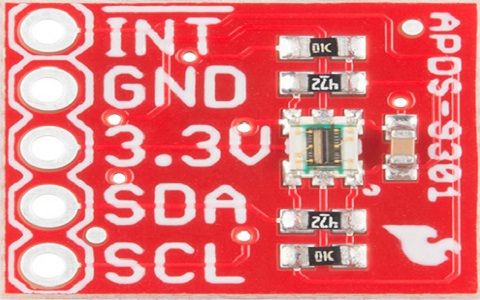

Seriell I / O-styrenhet för I2C-buss

Varje mikrokontroller från LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 inkluderar två I2C bussregulatorer, och detta är dubbelriktat. Inter-IC-kontrollen kan göras med hjälp av två ledningar, nämligen en SCL och SDA. Här är SDA & SCL seriell klocklinje och seriell datalinje

Varje apparat identifieras av en individuell adress. Här kan sändare och mottagare fungera i två lägen som huvudläge / slavläge. Detta är en multi-master-buss, och den kan hanteras av en eller flera bussmästare kopplade till den. Dessa mikrokontroller stödjer upp till 400 kbit / s bithastigheter.

SPI Serial Input / Output Controller

Dessa mikrokontroller inkluderar en enda SPI-kontroller och är avsedd att hantera många mästare och slavar som är associerade med en specifik buss.

Helt enkelt en mästare & en slav kan konversera över gränssnittet under specificerad dataöverföring. Under detta överför mastern ständigt en byte-of-data till slaven, liksom slaven överför ständigt data till master.

SSP Serial Input / Output Controller

Dessa mikrokontroller innehåller en enda SSP, och den här styrenheten kan bearbetas på en SPI, Microwire-buss eller 4-tråds SSI. Det kan kommunicera med flera mästares bussar och slavar

Men helt enkelt en viss mästare, såväl som en slav, kan samtala på bussen genom en specifik datasändning. Denna mikrokontroller stöder överföringar i full duplex, med 4-16 bitars dataramar som används för dataflödet från master-slaven såväl som från slaven-master.

Timers / Counters

Tidtagare och räknare är utformade för att räkna PCLK (perifer klocka) cykler och producerar valfritt avbrott baserat på 4-matchregister.

Och den består av fyra fångst i / ps för att fånga värdet på en timer när en i / p-signal ändras. Flera stift kan väljas för att utföra en viss fångst. Dessa mikrokontroller kan beräkna yttre händelser på ingångarna för fångst om minsta yttre puls är ekvivalent. I detta arrangemang kan lediga infångningslinjer väljas som vanliga timerfångare i / ps.

Vakthundstimer

Övervakningstimern används för att återställa mikrokontrollern på en rimlig tid. När det är tillåtet kommer timern att producera en återställning av ett system om konsumentprogrammet inte lyckas ladda om timern på en fast summa tid.

RTC-realtidsklocka

RTC är avsedd att tillhandahålla räknare för att beräkna tiden när tomgång eller normal driftsmetod väljs. RTC använder en liten mängd ström och är utformad för lämpliga batteridrivna arrangemang där den centrala processorenheten inte fungerar ständigt

Maktkontroll

Dessa mikrokontroller stödjer två kondenserade energilägen, t.ex. avstängningsläge och viloläge. I viloläge balanseras utförandet av instruktioner tills ett avbrott eller RST inträffar. Funktionerna för kringutrustning upprätthåller drift i viloläge och kan ge avbrott för att CPU ska starta om efterbehandling. I viloläge tas bort strömmen som används av CPU, styrenheter, minnessystem och inre bussar.

I avstängningsläge avaktiveras oscillatorn och IC får inga inre klockor. De perifera registren, processorns tillstånd med register, inre SRAM-värden sparas under avstängningsläge och chiplogiknivåernas utgångsstift stannar kvar.

Detta läge kan avslutas och den gemensamma processen startas om med specifika avbrott som kan fungera utan klockor. Eftersom chipoperationen är balanserad minskar Power-down-läget chipeffektutnyttjandet till nästan noll.

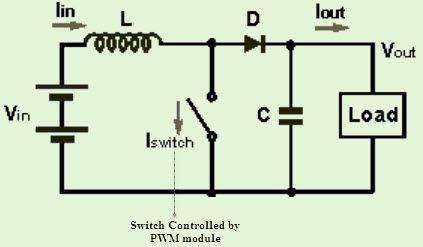

PWM-pulsbreddsmodulator

PWM: erna är baserade på det normala timerblocket och kommer också in i alla funktioner, men helt enkelt är pulsbreddsmodulatorfunktionen fixerad på mikrokontroller som LPC2141 / 42/44/46/48.

Timern är avsedd att beräkna PCLK (perifer klocka) cykler och valfritt producera avbrott när vissa timervärden uppstår baserat på 7-matchregister och PWM-funktionen beror också på matchregisterhändelser.

Förmågan att individuellt styra ökande och minskande gränslägen gör att pulsbreddsmoduleringen kan användas för flera applikationer. Till exempel använder den typiska motorstyrningen med flerfas 3-icke-överlappande utgångar av PWM genom separat styrning av varje pulsbredd och position.

VPB-buss

VPB-avdelaren löser kopplingen mellan CCLK (processorklocka) och PCLK (klocka som används av kringutrustning). Denna avdelare används för två ändamål. Den första användningen är att leverera kringutrustning med den föredragna PCLK med VPB-buss så att de kan arbeta med den valda hastigheten för ARM-processorn. För att uppnå detta kan denna busshastighet reduceras klockfrekvensen för processorn från 1⁄ 2-1⁄ 4.

Eftersom den här bussen måste fungera exakt vid uppstart, och standardläget vid RST (återställning) är att bussen ska fungera med 1⁄ 4: e processorns klockfrekvens. Den andra användningen av detta är att möjliggöra energibesparingar när en applikation inte behöver någon kringutrustning för att arbeta med hela processorhastigheten. Eftersom VPB-avdelaren är associerad med utgången från PLL, förblir denna aktiv under ett viloläge.

Emulering och felsökning

Mikrokontrollern (LPC2141 / 42/44/46/48) håller emulering och felsökning genom seriell port-JTAG.En spårningsport möjliggör spårning av genomförandet av programmet. Spårningsfunktioner och felsökningskoncept multiplexeras med port1 och GPIO.

Kodsäkerhet

Kodsäkerhetsfunktionen för dessa mikrokontroller LPC2141 / 42/44/46/48 tillåter en funktion att kontrollera om den kan skyddas eller felsökas från inspektion.

Således handlar det här om ARM7-baserad LPC2148 mikrokontrollerarkitektur. Från ovanstående artikel kan vi slutligen dra slutsatsen att ARM är en arkitektur som används i många processorer såväl som mikrokontroller. Här är en fråga till dig, vad är arkitekturen för en ARM-processor?